# Sil3726 SATA Port Multiplier Data Sheet

Document # Sil-DS-0121-C1

## Silicon Image, Inc.

June, 2006

Silicon Image, Inc. reserves the right to make changes to the product(s) or specifications to improve performance, reliability, or manufacturability. Information furnished is believed to be accurate and reliable, but Silicon Image, Inc. shall not be responsible for any errors that may appear in this document. Silicon Image, Inc. makes no commitment to update or keep current the information contained in this document.

However, no responsibility is assumed for its use; or any infringement of patents or other rights of third parties, which may result from its use. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

Silicon Image, Inc. products are not designed or intended for use in Life Support Systems. A Life Support System is a product or system intended to support or sustain life, which if it fails, can be reasonably expected to result in significant personal injury or death. If Buyer or any of its direct or indirect customers applies any product purchased or licensed from Silicon Image, Inc. to any such unauthorized use, Buyer shall indemnify and hold Silicon Image, Inc., its affiliates and their respective suppliers, harmless against all claims, costs, damages and expenses arising directly or indirectly, out of any such unintended or unauthorized use, even if such claims alleges that Silicon Image, Inc. or any other person or entity was negligent in designing or manufacturing the product. Specifications are subject to change without notice

#### **Copyright Notice**

Copyright © 2006 Silicon Image, Inc. All rights reserved. These materials contain proprietary and confidential information (including trade secrets, copyright and other interests) of Silicon Image, Inc. You may not use these materials except only for your bona fide non-commercial evaluation of your potential purchase of products and/services from Silicon Image or its affiliates, and/or only in connection with your purchase of products and/or services from Silicon Image or its affiliates, and only in accordance with the terms and conditions herein. You have no right to copy, modify, transfer, sublicense, publicly display, create derivative works of or distribute these materials, or otherwise make these materials available, in whole or in part, to any third party.

#### **Trademark Acknowledgment**

Silicon Image™, VastLane™, SteelVine™, PinnaClear™, Simplay™, Simplay™, Satalink™, and TMDS™ are trademarks or registered trademarks of Silicon Image, Inc. in the United States and other countries. HDMI™, the HDMI logo and High-Definition Multimedia Interface™ are trademarks or registered trademarks of, and are used under license from, HDMI Licensing, LLC.

#### **Further Information**

To request other materials, documentation, and information, contact your local Silicon Image, Inc. sales office or visit the Silicon Image, Inc. web site at <a href="https://www.siliconimage.com">www.siliconimage.com</a>.

#### **Revision History**

| Revision | Date   | Comment                                                          |

|----------|--------|------------------------------------------------------------------|

| Α        | 4/2005 | Derived from preliminary specification rev. 0.51                 |

| В        | 6/2006 | Updated green package, Converted to standard format              |

| С        | 7/2006 | Datasheet is no longer under NDA, removed confidential markings. |

## **Table of Contents**

| Table of Contents                                        | 3              |

|----------------------------------------------------------|----------------|

| Table of Figures                                         | 5              |

| Table of Tables                                          | 5              |

| Overview                                                 | 6              |

| Description                                              | 6              |

| Features                                                 | 6              |

| Overall Features                                         |                |

| Robust, High Performance PHY Technology                  |                |

| Storage System Features                                  |                |

| Architecture Features                                    |                |

| Functional Block Diagram                                 |                |

| SATA Ports                                               |                |

| LED Modes                                                |                |

| Device/Host LED Modes                                    |                |

| System LED Modes                                         |                |

| High Speed Serial Interface Optimization                 |                |

| PHY Configuration Settings                               |                |

| Tx Eye Measurement                                       |                |

| GPIO Support                                             |                |

| BIST Support                                             |                |

| Serial ATA Power Mode Request                            |                |

| Device Enumeration Sequence                              |                |

| Storage Enclosure Support                                |                |

| Internal Register Space                                  |                |

| General Status and Control (GSCR) Registers              | 12             |

| Port Status and Control Registers (PSCR)                 | 17             |

| Device Initialization                                    |                |

| Auto-Initialization from the EEPROM                      | 20             |

| EEPROM Specifications                                    |                |

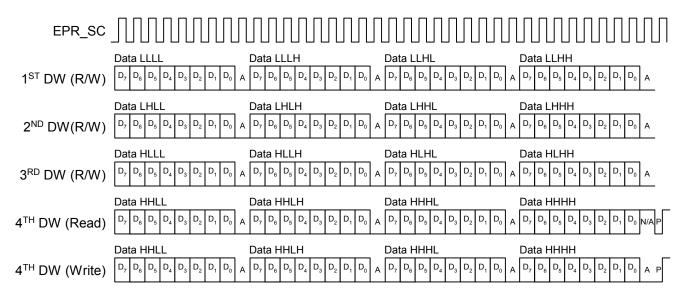

| EEPROM Read/Write Operations                             |                |

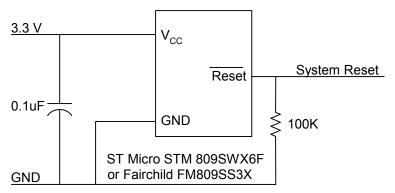

| System Reset                                             |                |

| Electrical Characteristics                               | 23             |

| Absolute Maximum Ratings                                 |                |

| DC Specifications                                        | 23             |

| SATA Interface DC Specifications                         | 24             |

| CLKI SerDes Input Reference Clock Requirements           |                |

| SATA Interface Timing Specifications                     |                |

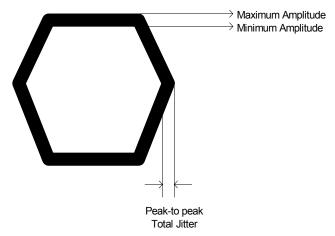

| SATA Interface Transmitter Output Jitter Characteristics | 26             |

| Pin Descriptions                                         | 27             |

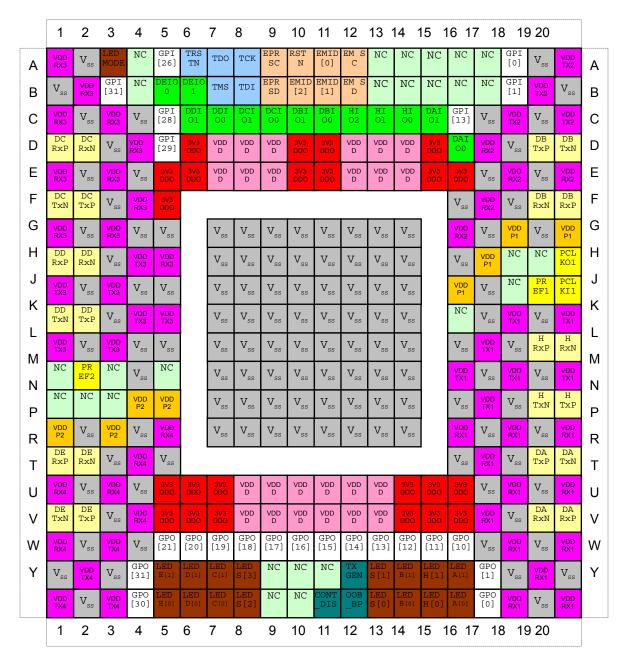

| Sil 3726 SATA Port Multiplier Pin-out                    | 27             |

| Package Pin Descriptions                                 | 37             |

| Pin Descriptions                                         | 37             |

| Package Information                                      | 38             |

| Dimensions                                               | 38             |

| © 2006 Silicon Image, Inc.                               | Sil-DS-0121-C1 |

# Sil3726 SATA Port Multiplier Data Sheet

| Silicon  | lmage, | Inc   |

|----------|--------|-------|

| JIIICUIT | imayc, | IIIC. |

| Part Ordering Numbers: | 39 |

|------------------------|----|

| References             | 40 |

# **Table of Figures**

| Figure 1: Sil 3726 SATA Port Multiplier Block Diagram  Figure 2: Enclosure Management Support Overview.  Figure 3: I <sup>2</sup> C Transfer Timing.  Figure 4: I <sup>2</sup> C Random Read and Write Timing.  Figure 5: I <sup>2</sup> C Block Transfer.  Figure 6: Power-Up Reset Circuit.  Figure 7: Eye Diagram.  Figure 8: Sil3726 Pinout Diagram. | 11<br>21<br>22<br>22<br>24 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

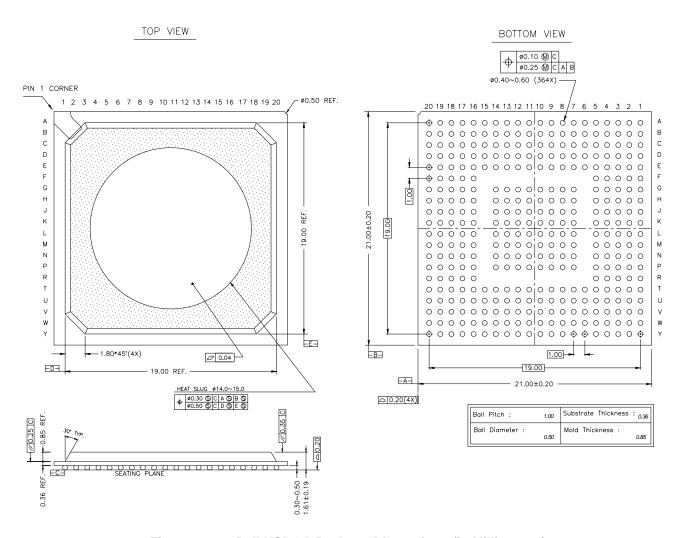

| Figure 9: 364 Ball HSBGA Package Dimensions (in Millimeters)                                                                                                                                                                                                                                                                                             |                            |

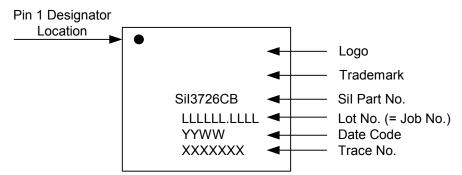

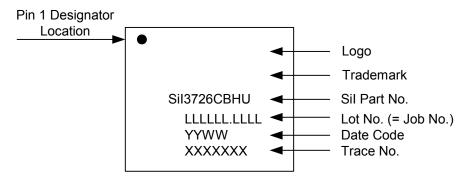

| Figure 10: Marking Specification - Sil3726CBFigure 11: Marking Specification - Sil3726CBHU                                                                                                                                                                                                                                                               |                            |

| Table 1: Device or Host LED Modes and Descriptions                                                                                                                                                                                                                                                                                                       | 8                          |

| Table 4: SError Bit Definitions                                                                                                                                                                                                                                                                                                                          |                            |

| Table 5: Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                        |                            |

| Table 6: DC Specifications                                                                                                                                                                                                                                                                                                                               |                            |

| Table 7: SATA Interface DC Specifications                                                                                                                                                                                                                                                                                                                |                            |

| Table 8: CLK1 SerDes Reference Clock Input Requirements                                                                                                                                                                                                                                                                                                  |                            |

| Table 9: SATA Interface Timing Specifications                                                                                                                                                                                                                                                                                                            | 25                         |

| Table 10: SATA Interface Transmitter Output Jitter Characteristics (1.5 G)                                                                                                                                                                                                                                                                               | 2620                       |

| Table 12: Sil3726 Pin List (Sorted by Pin Name)                                                                                                                                                                                                                                                                                                          |                            |

| Table 13: Sil3726 Pin List (Sorted by Pin Number)                                                                                                                                                                                                                                                                                                        |                            |

| Table 14: Power Supply Pin List                                                                                                                                                                                                                                                                                                                          |                            |

#### Overview

## Description

Silicon Images Sil 3726 SATA Port Multiplier is 1-to-5 SATA Port Multiplier designed to provide a high performance link between a single SATA host port and five SATA device ports. With its unique data aggregation capability and 3 Gbps serial link capability, the Sil 3726 SATA Port Multiplier is able to take full advantage of 3 Gbps host link bandwidth and FIS-based switching host controllers by bundling together data from device ports and sending it over the 3 Gbps host link. Additionally, the feature-rich Sil 3726 supports all the port multiplier related SATA II extensions allowing system designers to exploit the full potential of SATA in their storage solutions.

The Sil 3726 SATA Port Multiplier supports host and device link rates of 1.5 Gbps and 3 Gbps with autonegotiation allowing system designers to utilize 3 Gbps host links with today's 1.5 Gbps hard drives, and to future-proof designs for the emergence of 3 Gbps SATA hard drives. Additionally, the Sil 3726 contains a SATA Enclosure Management Bridge (SEMB) to pass in-band enclosure management information between the host and an enclosure management device. Other important features include, programmable high drive capability for backplane and external applications, asynchronous notification to eliminate the need for host polling to determine if a device has been added or removed, and hot plug support.

The Sil 3726 is designed for optimum power, performance and price. It is based on Silicon Images industry leading SATALink technology. It leverages much of the circuit innovation at the physical layer of Silicon Image's proprietary reduced-overhead Multi-layer Serial Link (MSLTM) architecture, which was pioneered and proven with our market-leading PanelLink® products. Silicon Image has shipped over 35 million units of PanelLink® products for host systems and displays in the PC and the CE markets, notable for their noisy operating conditions.

#### **Features**

#### **Overall Features**

- One-to-five native SATA Port Multiplier

- Full support for FIS-based switching and command-based switching SATA host controllers

- Advanced data aggregation architecture for ultra-fast read and write operations with FIS-based switching controllers

- 21mm x 21mm, 364 pin BGA package with a 20 x 20 array of balls

- High-speed, native SATA connections to host and device

- Host and device status and activity LEDs

#### Robust, High Performance PHY Technology

- 1.5 Gbps and 3.0 Gbps PHY support with auto-negotiation

- Compliant with SATA II external PHY specifications

- Independently programmable PHY settings to support extended PCB trace lengths and external SATA applications

- Industry proven SATALink technology

#### Storage System Features

- Hot-plug and ATAPI support

- SATA Enclosure Management Bridge (SEMB) support with I<sup>2</sup>C interface to the external Storage Enclosure Processor (SEP)

- Far-end Re-timed loop-back BIST for host initiated system testing

- Supports host control of hard disk drive staggered spin-up

- Asynchronous notification support

#### **Architecture Features**

- Features independent 8 kByte FIFO per device serial ATA channel for reads and writes

- High performance data movement between all SATA ports

## **Applications**

- Expansion Storage Bricks

- Disk Shelves

- Storage Enclosures

## **Functional Block Diagram**

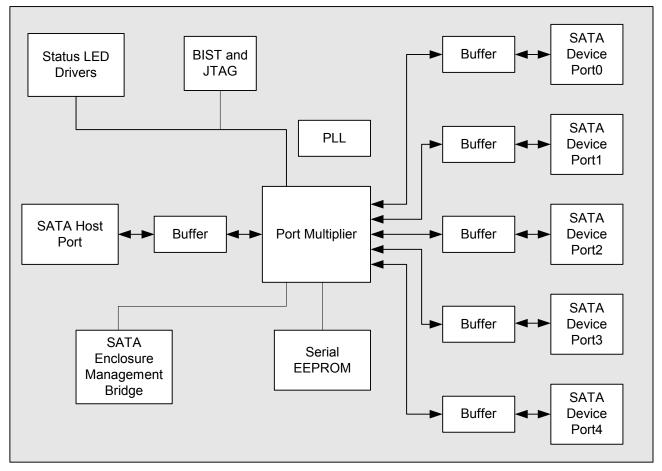

Figure 1 shows the Block Diagram for the Sil 3726 SATA Port Multiplier.

Figure 1: Sil 3726 SATA Port Multiplier Block Diagram

The following sections will describe the features of the port multiplier.

#### SATA Ports

The host port supports the SATA-II speed of 3 Gbps and auto-negotiates to 1.5 Gbps to interface with SATA-I host controllers. The device ports operate at SATA-II speeds of 3 Gbps or auto-negotiate to 1.5 Gbps. All ports support hot plug and extended (48 bit LBA) drive capability.

#### LED Modes

#### **Device/Host LED Modes**

Table 1 shows the device or host LED modes and descriptions. The mode is determined by the LED\_MODE pin (pin A3). LED pins are open-drain and sink current up to 12mA in their low voltage active state (LED On), or are high impedance in their high voltage non-active state (LED Off). These signals will operate with an external pull-up resistor and LED.

Each activity will turn on or off LED0 for approximately 70ms. The blinking rate is approximately 400ms on and 400ms off.

LED\_MODE LED1 LED0 Description Off Off 0 (PC mode) Power on, no device attached 0 (PC mode) On Off PHY communication established, (activity = LED0 On) 0 (PC mode) Blink Blink Error 1 (Enterprise mode) Off Off Power on, no device 1 (Enterprise mode) Off Error On

**Table 1: Device or Host LED Modes and Descriptions**

## **System LED Modes**

Table 2 shows the System LED modes and their descriptions.

Signal

LED\_S0

EEPROM load error

On: Loading error

Off: No loading errors

LED\_S1

System ready

On: System is ready

Off: System is not ready

LED\_S2

System error

On: System error

On: System error

On: System error

Off: No system error

Off: No system errors

**Table 2: System LED Modes and Descriptions**

In normal operation, if system reset is released, LED\_S3 will turn-on while the firmware loads into the Sil 3726 SATA Port Multiplier (~ 1 second). When the firmware load is complete, LED\_S1 will turn-on indicating the system is ready to be used.

## High Speed Serial Interface Optimization

In order to accommodate different system environments, the port multiplier allows the designer to configure the device PHYs to support various cable/PCB lengths on each serial I/O independently.

#### **PHY Configuration Settings**

Table 3 shows the configuration settings and description for each high-speed serial port.

Pre-emphasis and equalization are used to compensate the signal degradation due to increased cable lengths. Without pre-emphasis or equalization, jitter at the receiver end will increase along with the increase of the cable length, causing signal degradation and Bit Error Rate problems. The effect may depend on the system environment. Factors such as cable quality, PCB implementation, receiver load, etc. all affect the signal quality. Please consult with Silicon Image's technical support department for more information.

**Serial Port** Signal **Settings and Description** HIO[2:0] = 0b000 (Default). PC motherboard to device applications up to 1m internal Host Port HIO[2:0] cable, external desktop up to 2m external cable ((2 Meter eSATA cable) or short backplane up to 18 inch of FR4 (0.012 mil trace width with 1 oz copper) HIO[2:0] = 0b001: Tx amplitude will be 100mV lager than 000 setting HIO[2:0] = 0b010 - 0b100 (Reserved, please consult with Silicon Image technical support for this detail): external desktop up to 4m external cable or short backplane up to 30 inch of FR4 (0.012 mil trace width with 1 oz copper) 0b 010: Only pre-emphasis enabled 0b 011: Only equalization enabled 0b111: Both pre-emphasis and equalization enabled HIO[2:0] = 0b101 - 0b111 (Reserved, Contact Silicon Image Technical Support for details): external desktop longer than 4m external cable or short backplane longer than 30 inch of FR4 (0.012 mil trace width with 1 oz copper) 0b010: Only pre-emphasis enabled 0b011: Only equalization enabled 0b111: Both pre-emphasis and equalization enabled DAIO[1:0] DxIO[1:0] = 0b00 (Default): PC motherboard to device applications up to 1m internal Device #0 cable, external desktop up to 2m external cable (2 Meter eSATA cable) or short Device #1 DBIO[1:0] backplane up to 18 inch of FR4 (0.012 mil trace width with 1 oz copper) Device #2 DCIO[1:0] DxIO[1:0] = 0b01: Tx amplitude will be 100mV lager than 00 setting Device #3 DDIO[1:0] DxIO[1:0] = 0b10 (Reserved. Contact Silicon Image Technical Support): external desktop DEIO[1:0] Device #4 up to 4m external cable or short backplane up to 30 inch of FR4 (0.012 mil trace width with 1 oz copper). Both pre-emphasis and equalization are enabled DxIO[1:0] = 0b11 (Reserved. Contact Silicon Image Technical Support): external desktop longer than 4m external cable or short backplane longer than 30 inch of FR4 (0.012 mil trace width with 1 oz copper). Both pre-emphasis and equalization are enabled

Table 3: PHY Configuration Settings

#### Tx Eve Measurement

The Sil 3726 SATA Port Multiplier has the capability to output random (scrambled) and deterministic data patterns (primitives) to downstream devices bypassing the OOB sequence for eye measurement testing.

Upon completing the device enumeration process, the port multiplier outputs COM\_RESET/COMINIT periodically. This implementation maintains compatibility with the SATA compliant host/device and enables hot plug support. But this implementation also prevents evaluating the Tx eye quality by connecting it directly to the oscilloscope.

By bypassing the OOB sequence after the host completes the device enumeration sequence, the Tx will output a random data pattern. The port multiplier can bypass the OOB sequence by setting pin Y12 (OOB\_BP) to high. In addition to this, if CONT primitive is disabled by setting pin Y11 (CONT\_DIS) to high, the Tx will output a deterministic data pattern. The output generation (1.5 G or 3.0 G) can be selected by pin W12 (TX GEN).

The random data pattern is a scrambled data pattern and useful for eye mask testing. The deterministic pattern is a repetitive pattern of primitives and is useful for jitter analysis. The primitive is normally synchronous and includes Align primitives every 256DWORDs.

## **GPIO Support**

The 32 bits in General Status and Control Register [130] each correspond to its associated General Purpose Output pin on a write (GPO[31:0]). If the bit is set to 0, the GPO will output a high logic level. Bits [2:9] and [22:29] are not assigned to the pins and the value in the bit field does not effect the operation.

The 32 bits in General Status and Control Register [130] each correspond to its associated General Purpose Input pin on a read (GPI[31:0]). If the GPI1 is high, bit 1 will be set. Some of these GPI pins are reserved for various other functions as follows.

- Bit fields [12:10 / EMID [2:0]

- Bit fields [9:2] / 1000 0000b

- Bit fields [24:14] / DEIO[1], DDIO[0], DCIO[1:0], DBIO[1:0], DAIO[1:0]

- Bits 27 and 25 / DEIO[0], DDIO[1]

GPI pins have internal pull-downs, and GPO pins are initialized to drive low by the firmware.

The Read/Write Port Multiplier command can be used to read or write the GSCR. Address 0x0F must be specified in PortNum field of the command FIS in order to read or write the GSCR. The details of the Read/Write Port Multiplier commands are defined in the SATA II Port Multiplier Specification.

#### **BIST Support**

The Sil 3726 SATA Port Multiplier supports far-end retimed loopback BIST only as a target as described by the SATA II Port Multiplier Specification. If the port multiplier receives a BIST activated FIS, it enters BIST mode and loops back the SATA interface. The port multiplier does not propagate the BIST activated FIS to the other ports.

#### Serial ATA Power Mode Request

Either the host or the devices may initiate power mode requests. If the request is initiated by the device, upon receipt of the appropriate PMREQ\_P or PMREQ\_S) request, the port multiplier sends back the PMACK primitives and disables the TxP/TxN pair for the port.

If the request is initiated by the host, the port multiplier sends back the PMACK primitives and disables the TxP/TxN pair for the host port. The port multiplier issues the PMREQ to the all attached devices. Upon receipt of PMACK primitives from the physical devices, the TxP/TxN pair will be disabled.

## Device Enumeration Sequence

The device enumeration process is defined in the SATA II Port Multiplier Specification.

Upon receipt of the software reset with 0x0F as the PM port number, the Sil 3726 SATA Port Multiplier issues a Register Frame Information Structure (FIS) with the Port Multiplier Signature. Before receiving the software reset with 0x0F as the PM port number, the port multiplier delivers all Frame Information Structures to port 0 regardless of the PM port number value in the receiving FIS.

After sending the software reset with 0x0F as the PM port number, the PM aware host resets each device port by programming bit 1 in the SControl register and writing 0xFFFF\_FFFF in the SError register to clear the bits in the register.

The host should examine the SStatus and SError registers to determine whether or not a device is connected to the device ports. If a device is attached to the port, the host should initialize the device before it using it for a read or a write operation.

### Storage Enclosure Support

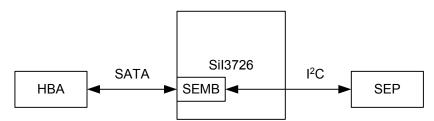

The Sil 3726 SATA Port Multiplier is compliant with the SATA II port multiplier specification. It has a SATA Enclosure Management Bridge (SEMB) that passes in-band enclosure management data between the host controller and a companion enclosure management device through an I<sup>2</sup>C bus.

Figure 2: Enclosure Management Support Overview

The port multiplier supports the SAF-TE and SES protocols. The host issues Enclosure Management commands through the SATA interface. Enclosure Management commands use the SEP\_ATTN commands in the Command register and the SEP command code in the Features register. The SEP command protocol is defined in the SAF-TE or SES specification.

The I<sup>2</sup>C interface is multi-master capable and can transfer data at 0 - 400 kbits/s. The SEMB I<sup>2</sup>C address is 0001xxx0, where xxx are selected using pins EM\_ID[2:0]. This allows up to eight SiI 3726 SATA Port Multipliers on the same SEMB I<sup>2</sup>C bus. The SEP I<sup>2</sup>C address should be 0xC0, as defined in the SATA II specification.

## **Internal Register Space**

The Sil 3726 SATA Port Multiplier has 32-bit wide registers that control its internal operations.

## General Status and Control (GSCR) Registers

These registers are defined in the SATA II Port Multiplier specification.

The Read/Write Port Multiplier command is used to read or write the GSCR registers. Address 0x0F must be specified in the PortNum field of the command FIS in order to read or write the GSCR. The Read/Write Port Multiplier commands are defined in the SATA II Port Multiplier Specification.

|          | Addr             | Name            | 31                    | 30                                                                          | 29           | 28           | 27        | 26          | 25   | 24      |

|----------|------------------|-----------------|-----------------------|-----------------------------------------------------------------------------|--------------|--------------|-----------|-------------|------|---------|

|          | 0x00             | Product         |                       |                                                                             |              | Dev          | ice ID    |             |      |         |

| GS       | GSCR[00]         |                 | 23 22 21 20 19 18 17  |                                                                             |              |              |           |             |      | 16      |

|          |                  |                 |                       |                                                                             |              | Dev          | ice ID    |             |      |         |

|          |                  |                 | 15                    | 14                                                                          | 13           | 12           | 11        | 10          | 9    | 8       |

|          |                  |                 |                       | Vendor ID                                                                   |              |              |           |             |      |         |

|          |                  |                 | 7                     | 6                                                                           | 5            | 4            | 3         | 2           | 1    | 0       |

|          |                  |                 |                       |                                                                             |              | Ven          | dor ID    |             |      |         |

| Bit      | Label            | R/W             |                       |                                                                             |              | Description  | n         |             |      | Default |

| This reg | jister defines t | he Device ID ar | nd Vendor I           | D associat                                                                  | ted with the | Sil 3726.    |           |             |      |         |

| 31:16    | Device ID        | R               | The defau<br>Sil3726. | The default value of 0x3726 identifies the device as Silicon Image Sil3726. |              |              |           |             |      |         |

| 15:0     | Vendor ID        | R               | This field            | defaults to                                                                 | 0x1095 to    | identify the | vendor as | Silicon Ima | age. | 0x1095  |

| 4                                                                  | Addr                                  | Name        | 31 30 29 28 27 26 25 |                                                                                                                                                                               |             |             |             |      |    | 24      |  |

|--------------------------------------------------------------------|---------------------------------------|-------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|------|----|---------|--|

| (                                                                  | 0x01                                  | Revision    |                      |                                                                                                                                                                               |             | RS          | VD0         |      |    |         |  |

| GS                                                                 | CR[01]                                | Information | 23                   | 22                                                                                                                                                                            | 21          | 20          | 19          | 18   | 17 | 16      |  |

|                                                                    |                                       |             | RSVD0                |                                                                                                                                                                               |             |             |             |      |    |         |  |

|                                                                    |                                       |             | 15                   | 14                                                                                                                                                                            | 13          | 12          | 11          | 10   | 9  | 8       |  |

|                                                                    |                                       |             |                      |                                                                                                                                                                               | Re          | vision ID/C | hip Revisio | n ID |    |         |  |

|                                                                    |                                       |             | 7                    | 6                                                                                                                                                                             | 5           | 4           | 3           | 2    | 1  | 0       |  |

|                                                                    |                                       |             | RSVD0 PM spec        |                                                                                                                                                                               |             |             |             |      |    | RSVD0   |  |

| Bit                                                                | Label                                 | R/W         |                      | Description                                                                                                                                                                   |             |             |             |      |    |         |  |

| This register defines the revision ID associated with the Sil3726. |                                       |             |                      |                                                                                                                                                                               |             |             |             |      |    |         |  |

| 31:16                                                              | RSVD0                                 | R           | This bit fie         | eld is reser                                                                                                                                                                  | ved and ref | urns a zero | value.      |      |    | 0x0000  |  |

| 15:8                                                               | Revision<br>ID/Chip<br>Revision<br>ID | R           |                      | This bit field is set to indicate the revision level of the chip design, revision 0x17 is defined by this specification.                                                      |             |             |             |      |    |         |  |

| 7:3                                                                | RSVD0                                 | R           | This bit fie         | eld is reser                                                                                                                                                                  | ved and ref | urns a zero | value.      |      |    | 0b00000 |  |

| 2:1                                                                | PM spec                               | R           | field is se          | This register defines the Port Multiplier Specification Supports. This bit field is set to 0x11 to indicate that Sil 3726 supports the Port Multiplier Specification and 1.1. |             |             |             |      |    |         |  |

| 0                                                                  | RSVD0                                 | R           | This bit fie         | eld is reser                                                                                                                                                                  | ved and ref | urns a zero | value.      |      |    | 0b0     |  |

|          | Addr             | Name             | 31           | 30                                                                           | 29         | 28           | 27     | 26        | 25         | 24      |  |

|----------|------------------|------------------|--------------|------------------------------------------------------------------------------|------------|--------------|--------|-----------|------------|---------|--|

|          | 0x02             | Port             |              |                                                                              |            | RS           | VD0    |           |            |         |  |

| GS       | SCR[02]          | Information      | 23           | 22                                                                           | 21         | 20           | 19     | 18        | 17         | 16      |  |

|          |                  |                  |              |                                                                              |            | RS           | VD0    |           |            |         |  |

|          |                  |                  | 15           | 14                                                                           | 13         | 12           | 11     | 10        | 9          | 8       |  |

|          |                  |                  |              | RSVD0                                                                        |            |              |        |           |            |         |  |

|          |                  |                  | 7            | 6                                                                            | 5          | 4            | 3      | 2         | 1          | 0       |  |

|          |                  |                  |              | RS                                                                           | VD0        |              | ١      | Number of | Fan-out po | rts     |  |

| Bit      | Label            | R/W              |              |                                                                              |            | Description  | 1      |           |            | Default |  |

| This reg | gister defines ¡ | oort information | associated   | with the S                                                                   | il3726.    |              |        |           |            |         |  |

| 31:4     | RSVD0            | R                | This bit fie | eld is reser                                                                 | ved and re | turns a zero | value. |           |            | 0x0000  |  |

|          |                  |                  |              |                                                                              |            |              |        |           |            |         |  |

| 3:0      | Number of        | R                |              | This bit field is set to 0x06 to indicate that Sil3726 supports one host and |            |              |        |           |            |         |  |

|          | Fan-out          |                  | five device  | e ports.                                                                     |            |              |        |           |            |         |  |

|          | ports            |                  |              |                                                                              |            |              |        |           |            |         |  |

|       | Addr        | Name        | 31                  | 30           | 29           | 28           | 27          | 26       | 25       | 24       |  |

|-------|-------------|-------------|---------------------|--------------|--------------|--------------|-------------|----------|----------|----------|--|

|       | 0x20        | Error       |                     |              |              | RSV          | 'DRW        |          |          |          |  |

| GS    | SCR[32]     | Information | 23                  | 22           | 21           | 20           | 19          | 18       | 17       | 16       |  |

|       |             |             |                     |              |              | RSV          | 'DRW        |          |          |          |  |

|       |             |             | 15                  | 14           | 13           | 12           | 11          | 10       | 9        | 8        |  |

|       |             |             |                     |              |              | RSV          | 'DRW        |          |          |          |  |

|       |             |             | 7                   | 6            | 5            | 4            | 3           | 2        | 1        | 0        |  |

|       |             |             | RSVI                | DRW          | Error        | Error        | Error       | Error    | Error    | Error    |  |

|       |             |             |                     |              | Informat     | Informat     | Informat    | Informat | Informat | Informat |  |

|       |             |             | ion ion ion ion ion |              |              |              |             |          |          | ion      |  |

| Bit   | Label       | R/W         |                     | Description  |              |              |             |          |          |          |  |

| 31:06 | RSVDRW      | R/W         | This bit fie        | eld is reser | ved and ref  | turns the va | lue written | to it.   |          | 0x0000   |  |

| 5     | Error       | R/W         |                     |              | hen the bits |              |             |          | are set. | 0b0      |  |

|       | Information |             | The bits u          | ised for thi | s bit are se | lected by th | e GSCR[33   | 3]       |          |          |  |

| 4     | Error       | R/W         |                     |              | hen the bits |              |             |          | are set. | 0b0      |  |

|       | Information |             |                     |              | s bit are se |              |             | -        |          |          |  |

| 3     | Error       | R/W         |                     |              | hen the bits |              |             |          | are set. | 0b0      |  |

|       | Information |             |                     |              | s bit are se |              | •           | •        |          |          |  |

| 2     | Error       | R/W         |                     |              | hen the bits |              |             |          | are set. | 0b0      |  |

|       | Information |             |                     |              | s bit are se |              | -           | -        |          |          |  |

| 1     | Error       | R/W         |                     |              | hen the bits |              |             |          | are set. | 0b0      |  |

|       | Information |             |                     |              | s bit are se |              |             | •        |          |          |  |

| 0     | Error       | R/W         |                     |              | hen the bits |              |             |          | are set. | 0b0      |  |

|       | Information |             | The bits u          | ised for thi | s bit are se | ected by th  | e GSCR[33   | <u> </u> |          |          |  |

|          | Addr                 | Name        | 31                | 30                                                                                                                                                                  | 29 | 28         | 27        | 26 | 25 | 24      |  |

|----------|----------------------|-------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------|-----------|----|----|---------|--|

| 0x21     |                      | Error       | Error Information |                                                                                                                                                                     |    |            |           |    |    |         |  |

| GSCR[33] |                      | Information | 23                | 22                                                                                                                                                                  | 21 | 20         | 19        | 18 | 17 | 16      |  |

|          |                      |             |                   |                                                                                                                                                                     |    | Error In   | formation |    |    |         |  |

|          |                      |             | 15                | 14                                                                                                                                                                  | 13 | 12         | 11        | 10 | 9  | 8       |  |

|          |                      |             | Error Information |                                                                                                                                                                     |    |            |           |    |    |         |  |

|          |                      |             | 7                 | 6                                                                                                                                                                   | 5  | 4          | 3         | 2  | 1  | 0       |  |

|          |                      |             | Error Information |                                                                                                                                                                     |    |            |           |    |    |         |  |

| Bit      | Label                | R/W         |                   |                                                                                                                                                                     |    | Descriptio | n         |    |    | Default |  |

| 31:0     | Error<br>Information | R/W         | Error Info        | This bit field provides the bits used for error information in the GSCR[32] Error Information register. If the bit set to 1, that bit will be used by the GSCR[32]. |    |            |           |    |    |         |  |

|      | Addr                                            | Name     | 31 30 29 28 27 26 25                                                            |                                                                                                       |               |              |             |            |                 |     |  |  |

|------|-------------------------------------------------|----------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------|--------------|-------------|------------|-----------------|-----|--|--|

|      | 0x40                                            | Optional |                                                                                 |                                                                                                       |               | RS           | SVD0        |            |                 |     |  |  |

| GS   | SCR[64]                                         | Features | 23                                                                              | 22                                                                                                    | 21            | 20           | 19          | 18         | 17              | 16  |  |  |

|      |                                                 | Support  |                                                                                 | RSVD0                                                                                                 |               |              |             |            |                 |     |  |  |

|      |                                                 |          | 15                                                                              | 14                                                                                                    | 13            | 12           | 11          | 10         | 9               | 8   |  |  |

|      |                                                 |          |                                                                                 |                                                                                                       |               | RS           | SVD0        |            |                 |     |  |  |

|      |                                                 |          | 7                                                                               | 6                                                                                                     | 5             | 4            | 3           | 2          | 1               | 0   |  |  |

|      |                                                 |          | RSVD0  Async notificati c SSC PMREQ on Transmi support t Enable support support |                                                                                                       |               |              |             |            | BIST<br>support |     |  |  |

| Bit  | Label                                           | R/W      |                                                                                 | Description                                                                                           |               |              |             |            |                 |     |  |  |

| 31:4 | RSVD0                                           | R        | This bit fie                                                                    | This bit field is reserved and returns a zero value.                                                  |               |              |             |            |                 |     |  |  |

| 3    | Async notification support                      | R        | This bit fie notificatio                                                        |                                                                                                       | 1 to indica   | ite that the | Sil3726 sup | ports Asyn | chronous        | 0b1 |  |  |

| 2    | Dynamic<br>SSC<br>Transmit<br>Enable<br>support | R        |                                                                                 | This bit field is set to 0 to indicate that the Sil3726 does not support Dynamic SSC Transmit Enable. |               |              |             |            |                 |     |  |  |

| 1    | Issuing<br>PMREQ_<br>P to host<br>support       | R        |                                                                                 | This bit field is set to 0 to indicate that the Sil3726 does not support issuing PMREQ_P to host.     |               |              |             |            |                 |     |  |  |

| 0    | BIST<br>support                                 | R        | This bit fie                                                                    | eld is set to                                                                                         | o 1 to indica | ite that the | Sil3726 sup | ports BIST |                 | 0b1 |  |  |

|       | Addr                                       | Name               | 31           | 30                                                                                                           | 29         | 28          | 27        | 26                                   | 25                              | 24             |  |  |

|-------|--------------------------------------------|--------------------|--------------|--------------------------------------------------------------------------------------------------------------|------------|-------------|-----------|--------------------------------------|---------------------------------|----------------|--|--|

|       |                                            | 11001110           | 31           | 30                                                                                                           | 29         |             |           | 20                                   | 23                              | 24             |  |  |

|       | 0x60                                       | Optional           |              | 1                                                                                                            |            |             | SVD0      |                                      |                                 |                |  |  |

| GS GS | SCR[96]                                    | Features<br>Enable | 23           | 22                                                                                                           | 21         | 20          | 19        | 18                                   | 17                              | 16             |  |  |

|       |                                            | Lilable            |              | RSVD0                                                                                                        |            |             |           |                                      |                                 |                |  |  |

|       |                                            |                    | 15           | 15   14   13   12   11   10   9                                                                              |            |             |           |                                      |                                 |                |  |  |

|       |                                            |                    | RSVD0        |                                                                                                              |            |             |           |                                      |                                 |                |  |  |

|       |                                            |                    | 7            | 6                                                                                                            | 5          | 4           | 3         | 2                                    | 1                               | 0              |  |  |

|       |                                            |                    |              | RSVD0                                                                                                        |            |             |           | Enable<br>Dynamic<br>SSC<br>Transmit | Enable issuing PMREQ _P to host | Enable<br>BIST |  |  |

| Bit   | Label                                      | R/W                |              | Description                                                                                                  |            |             |           |                                      |                                 |                |  |  |

| 31:4  | RSVD0                                      | R                  | This bit fie | This bit field is reserved and returns a zero value.                                                         |            |             |           |                                      |                                 |                |  |  |

| 3     | Enable<br>Asynchron<br>ous<br>notification | R                  | Setting th   | is bit enab                                                                                                  | les Asynch | ronous noti | fication. |                                      |                                 | 0b0            |  |  |

| 2     | Enable<br>Dynamic<br>SSC<br>Transmit       | R                  |              | The Sil3726 does not support Dynamic SSC Transmit and setting this bit does not affect the operation.        |            |             |           |                                      |                                 |                |  |  |

| 1     | Enable issuing PMREQ_P to host             | R                  |              | The Sil3726 does not support issuing PMREQ_P to the host and setting this bit does not affect the operation. |            |             |           |                                      |                                 |                |  |  |

| 0     | Enable<br>BIST                             | R                  | Setting th   | is bit enab                                                                                                  | les BIST.  |             |           |                                      |                                 | 0b1            |  |  |

| 4    | Addr      | Name     | 31           | 30            | 29         | 28           | 27     | 26 | 25 | 24             |  |

|------|-----------|----------|--------------|---------------|------------|--------------|--------|----|----|----------------|--|

| 0x0  | 3 - 0x1F  | Reserved |              | RSVD0         |            |              |        |    |    |                |  |

| GSC  | R[03-31], |          | 23           | 22            | 21         | 20           | 19     | 18 | 17 | 16             |  |

| 0x2  | 2 - 0x3F  |          |              |               |            | RS           | VD0    |    |    |                |  |

| GSC  | R[34-63], |          | 15           | 14            | 13         | 12           | 11     | 10 | 9  | 8              |  |

| _    | 1 - 0x5F  |          |              |               |            | RS           | VD0    |    |    |                |  |

|      | R[65-95], |          | 7            | 7 6 5 4 3 2 1 |            |              |        |    |    |                |  |

|      | 1 - 0x7F  |          |              |               |            | RS           | VD0    |    |    |                |  |

| GSC  | R[97-127] |          |              |               |            |              |        |    |    |                |  |

| Bit  | Label     | R/W      |              |               |            | Descriptio   | n      |    |    | Default        |  |

| 31:0 | RSVD0     | R        | This bit fie | eld is reser  | ved and re | turns a zero | value. |    |    | 0x0000<br>0000 |  |

|      | Addr       | Name   | 31        | 30                                                                    | 29         | 28           | 27       | 26 | 25 | 24     |

|------|------------|--------|-----------|-----------------------------------------------------------------------|------------|--------------|----------|----|----|--------|

| 0x8  | 0 - 0x81   | Vendor |           |                                                                       |            | Vendo        | r Unique |    |    |        |

| GSCF | R[128-129, | Unique | 23        | 22                                                                    | 21         | 20           | 19       | 18 | 17 | 16     |

| 3x0  | 33 - 0xFF  |        |           |                                                                       |            | Vendo        | r Unique |    |    |        |

| GSCF | R[131-255] |        | 15        | 15 14 13 12 11 10 9                                                   |            |              |          |    |    |        |

|      |            |        |           | Vendor Unique                                                         |            |              |          |    |    |        |

|      |            |        | 7         | 7 6 5 4 3 2 1                                                         |            |              |          |    |    | 0      |

|      |            |        |           |                                                                       |            | Vendo        | r Unique |    |    |        |

| Bit  | Label      | R/W    |           | Description                                                           |            |              |          |    |    |        |

| 31:0 | Vendor     | R/W    | These reg | These registers define vendor unique and may be used by the firmware. |            |              |          |    |    | 0x0000 |

|      | Unique     |        | The user  | shall not a                                                           | ccess thes | e registers. |          |    |    | 0000   |

|      | Addr    | Name | 31                                | 30                                                                                                                                                                                                                                                                                                                                                             | 29 | 28         | 27  | 26 | 25 | 24      |  |

|------|---------|------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------|-----|----|----|---------|--|

|      | 0x82    | GPIO |                                   |                                                                                                                                                                                                                                                                                                                                                                |    | G          | PIO |    |    |         |  |

| GS   | CR[130] |      | 23                                | 22                                                                                                                                                                                                                                                                                                                                                             | 21 | 20         | 19  | 18 | 17 | 16      |  |

|      |         |      |                                   | GPIO                                                                                                                                                                                                                                                                                                                                                           |    |            |     |    |    |         |  |

|      |         |      | 15                                | 15 14 13 12 11 10 9                                                                                                                                                                                                                                                                                                                                            |    |            |     |    |    |         |  |

|      |         |      |                                   | GPIO                                                                                                                                                                                                                                                                                                                                                           |    |            |     |    |    |         |  |

|      |         |      | 7                                 | 7 6 5 4 3 2 1                                                                                                                                                                                                                                                                                                                                                  |    |            |     |    |    |         |  |

|      |         |      |                                   |                                                                                                                                                                                                                                                                                                                                                                |    | G          | PIO |    |    |         |  |

| Bit  | Label   | R/W  |                                   |                                                                                                                                                                                                                                                                                                                                                                |    | Descriptio | n   |    |    | Default |  |

| 31:0 | GPIO    | R/W  | the GPO<br>a read. If<br>downs, a | The bit field is corresponding to the GPO pins on a write. If the bit 0 is set, the GPO 0 will output high. The bit field is corresponding to the GPI pins on a read. If the GPI 1 is high, the bit 1 will be set. GPI pins have internal pull-lowns, and GPO pins will be initialized to drive low by the firmware. For letails, see GPIO Support on page 10. |    |            |     |    |    |         |  |

# Port Status and Control Registers (PSCR)

The registers are defined in the SATA II Extensions to Serial ATA 1.0a Specification.

The Read/Write Port Multiplier command may be used to read or write the PSCR. The port number must be specified in the PortNum field of the command FIS in order to read or write the PSCR. The Read/Write Port Multiplier commands are defined in the SATA II Port Multiplier specification.

|       | Addr    | Mama    | 24                                                         | 20                                                                                                                                                                                                                                                                                  | 20                                                    | 20                                          | 27                                             | 20                                                                 | 25               | 24          |  |

|-------|---------|---------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------|------------------------------------------------|--------------------------------------------------------------------|------------------|-------------|--|

|       |         | Name    | 31                                                         | 1 30 29 28 27 26 25 RSVD0                                                                                                                                                                                                                                                           |                                                       |                                             |                                                |                                                                    |                  |             |  |

|       | 0x00    | SStatus |                                                            |                                                                                                                                                                                                                                                                                     |                                                       |                                             |                                                |                                                                    |                  |             |  |

| PS    | SCR[00] |         | 23                                                         | 22                                                                                                                                                                                                                                                                                  | 21                                                    | 20                                          | 19                                             | 18                                                                 | 17               | 16          |  |

|       |         |         |                                                            |                                                                                                                                                                                                                                                                                     |                                                       | RS                                          | SVD0                                           |                                                                    |                  |             |  |

|       |         |         | 15                                                         | 14                                                                                                                                                                                                                                                                                  | 13                                                    | 12                                          | 11                                             | 10                                                                 | 9                | 8           |  |

|       |         |         |                                                            | RS                                                                                                                                                                                                                                                                                  | SVD0                                                  |                                             |                                                | IP                                                                 | M                |             |  |

|       |         |         | 7                                                          | 6                                                                                                                                                                                                                                                                                   | 5                                                     | 4                                           | 3                                              | 2                                                                  | 1                | 0           |  |

|       |         |         |                                                            | S                                                                                                                                                                                                                                                                                   | SPD                                                   |                                             |                                                | DE                                                                 | ĒΤ               |             |  |

| Bit   | Label   | R/W     |                                                            | Description                                                                                                                                                                                                                                                                         |                                                       |                                             |                                                |                                                                    |                  |             |  |

| 31:12 | RSVD0   | R       | This bit fi                                                | eld is rese                                                                                                                                                                                                                                                                         | rved and re                                           | turns a zero                                | value.                                         |                                                                    |                  | 0x0000<br>0 |  |

| 11:08 | IPM     | R       | 0000: De<br>0001: Inte<br>0010: Inte<br>0110: Inte         | This field identifies the current interface power management state.  000: Device not present or communicating not established  001: Interface in active state  010: Interface in partial power management state  110: Interface in slumber power management state  Others: Reserved |                                                       |                                             |                                                |                                                                    |                  |             |  |

| 7:4   | SPD     | R       | 0000: No<br>0001: Ge                                       | negotiated<br>neration 1<br>neration 2                                                                                                                                                                                                                                              | •                                                     | ation rate (1                               | .5 Gb/s)                                       | cation speed                                                       |                  | 0x0         |  |

| 3:0   | DET     | R       | 0000: No<br>0001: De<br>0010: De<br>0110: PH<br>running ir | device de<br>vice prese<br>vice prese<br>Y in off-lin                                                                                                                                                                                                                               | nce detecte<br>nce detecte<br>e mode as<br>oopback mo | PHY commed, but PHYed and PHYaresult of the | unication no<br>communication<br>communication | PHY state.  pt establishe ation not est ation establis being disab | ablished<br>shed | 0x0         |  |

|       | Addr   | Name   | 31                                     | 30                                                                                                                                                                                                                                                                                                                                                                                | 29          | 28             | 27         | 26 | 25 | 24      |  |

|-------|--------|--------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|------------|----|----|---------|--|

|       | 0x01   | SError |                                        |                                                                                                                                                                                                                                                                                                                                                                                   |             | DI             | AG         |    |    |         |  |