# MPEG Clock Generator with VCXO

#### **Features**

- Robust Oscillator

- · Low-jitter, high-accuracy outputs

- VCXO with analog adjust

- 3.3V operation

# Benefits

- Highest-performance oscillator tailored for multimedia applications

- Meets critical timing requirements in complex system designs

- · Application compatibility for a wide variety of designs

#### **Frequency Table**

| Part Number  | Outputs | Input Frequency Range                                   | Output Frequencies | VCXO Control<br>Curve | Other Features     |

|--------------|---------|---------------------------------------------------------|--------------------|-----------------------|--------------------|

| CY241V08A-02 |         | 27-MHz pullable crystal input per Cypress specification | One copy of 27 MHz | linear                | Low Jitter Non-PLL |

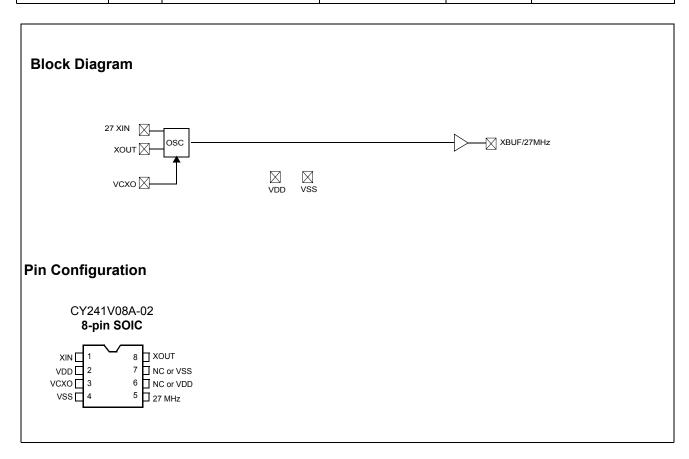

# **Pin Descriptions**

| Name        | Pin Number | Description                   |  |  |  |

|-------------|------------|-------------------------------|--|--|--|

| XIN         | 1          | Reference crystal input.      |  |  |  |

| VDD         | 2          | Voltage supply.               |  |  |  |

| VCXO        | 3          | t analog control for VCXO.    |  |  |  |

| VSS         | 4          | ound.                         |  |  |  |

| XBUF/27 MHz | 5          | -MHz buffered crystal output. |  |  |  |

| NC          | 6          | No Connect or VDD.            |  |  |  |

| NC          | 7          | o Connect or VSS              |  |  |  |

| XOUT        | 8          | Reference crystal output.     |  |  |  |

#### **Absolute Maximum Conditions**

| Supply Voltage (V <sub>DD</sub> )0.5 to +7.0V                                            |

|------------------------------------------------------------------------------------------|

| DC Input Voltage0.5V to V <sub>DD</sub> + 0.5                                            |

| Storage Temperature (Non-condensing)–55°C to +125°C                                      |

| Junction Temperature40°C to +125°C <b>Pullable Crystal Specifications</b> <sup>[1]</sup> |

| Data Retention @ Tj = 125°C                                       | > 10 years      |

|-------------------------------------------------------------------|-----------------|

| - ·                                                               | •               |

| Package Power Dissipation                                         |                 |

| ESD (Human Body Model) MIL-STD-883                                | > 2000V         |

| (Above which the useful life may be impaired. lines, not tested.) | For user guide- |

| Parameter                      | Description                                              | Comments                                                                             | Min. | Тур. | Max. | Unit |

|--------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| F <sub>NOM</sub>               | Nominal crystal frequency                                | Parallel resonance, fundamental mode, AT cut                                         | -    | 27   | -    | MHz  |

| C <sub>LNOM</sub>              | Nominal load capacitance                                 |                                                                                      | -    | 14   | -    | pF   |

| R <sub>1</sub>                 | Equivalent series resistance (ESR)                       | Fundamental mode                                                                     | _    | _    | 25   | Ω    |

| R <sub>3</sub> /R <sub>1</sub> | Ratio of third overtone mode ESR to fundamental mode ESR | Ratio used because typical R <sub>1</sub> values are much less than the maximum spec | 3    | _    | -    | _    |

| DL                             | Crystal drive level                                      | No external series resistor assumed                                                  | 150  | _    | -    | μW   |

| F <sub>3SEPHI</sub>            | Third overtone separation from 3*F <sub>NOM</sub>        | High side                                                                            | 300  | _    | -    | ppm  |

| F <sub>3SEPLO</sub>            | Third overtone separation from 3*F <sub>NOM</sub>        | Low side                                                                             | -    | _    | -150 | ppm  |

| C <sub>0</sub>                 | Crystal shunt capacitance                                |                                                                                      | -    | _    | 7    | pF   |

| C <sub>0</sub> /C <sub>1</sub> | Ratio of shunt to motional capacitance                   |                                                                                      | 180  | _    | 250  | _    |

| C <sub>1</sub>                 | Crystal motional capacitance                             |                                                                                      | 14.4 | 18   | 21.6 | fF   |

## **Recommended Operating Conditions**

| Parameter         | Description                                                                                                   | Min.  | Тур. | Max.  | Unit |

|-------------------|---------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| $V_{DD}$          | Operating Voltage                                                                                             | 3.135 | 3.3  | 3.465 | V    |

| T <sub>A</sub>    | Ambient Temperature                                                                                           | 0     | _    | 70    | °C   |

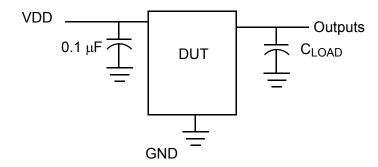

| C <sub>LOAD</sub> | Max. Load Capacitance                                                                                         | -     | _    | 15    | pF   |

| t <sub>PU</sub>   | Power-up time for all V <sub>DD</sub> pins to reach minimum specified voltage (power ramps must be monotonic) | 0.05  | -    | 500   | ms   |

## **DC Electrical Specifications**

| Parameter             | Name                   | Description                             | Min. | Тур. | Max.     | Unit |

|-----------------------|------------------------|-----------------------------------------|------|------|----------|------|

| I <sub>ОН</sub>       | Output HIGH Current    | $V_{OH} = V_{DD} - 0.5V, V_{DD} = 3.3V$ | 12   | 24   | _        | mA   |

| l <sub>OL</sub>       | Output LOW Current     | $V_{OL} = 0.5V, V_{DD} = 3.3V$          | 12   | 24   | _        | mA   |

| C <sub>IN</sub>       | Input Capacitance      | Except XIN, XOUT pins                   | _    | _    | 7        | pF   |

| V <sub>VCXO</sub>     | VCXO Input Range       |                                         | 0    | _    | $V_{DD}$ | V    |

| $f_{\Delta XO}^{[2]}$ | VCXO Pullability Range | Low Side                                | _    | _    | -115     | ppm  |

|                       |                        | High Side                               | 115  | _    | _        | ppm  |

| $I_{VDD}$             | Supply Current         |                                         | -    | _    | 35       | mA   |

## AC Electrical Specifications ( $V_{DD} = 3.3V$ ) [3]

| Parameter <sup>[3]</sup> | Name                       | Description                                                                                                            | Min. | Тур. | Max. | Unit |

|--------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

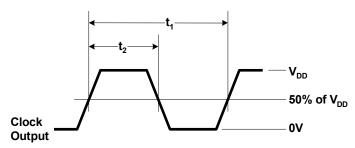

| DC                       | Output Duty Cycle          | Duty Cycle is defined in Figure 1, 50% of V <sub>DD</sub>                                                              | 45   | 50   | 55   | %    |

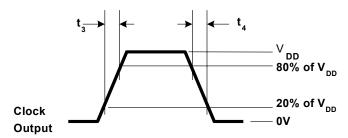

| ER                       | Rising Edge Rate           | Output Clock Edge Rate, Measured from 20% to 80% of V <sub>DD</sub> , C <sub>LOAD</sub> = 15 pF. See <i>Figure 2</i> . | 0.8  | 1.4  | -    | V/ns |

| EF                       | Falling Edge Rate          | Output Clock Edge Rate, Measured from 80% to 20% of V <sub>DD</sub> , C <sub>LOAD</sub> = 15 pF. See <i>Figure 2</i> . | 0.8  | 1.4  | -    | V/ns |

| t <sub>9</sub>           | Peak-to-peak Period Jitter | 27-MHz Clock Jitter                                                                                                    | _    | _    | 100  | ps   |

#### Notes:

- Crystals that meet this specification includes: Ecliptek ECX-5808-27.000M

-115/+115 ppm assumes 2.5 pF of additional board level load capacitance. This range will be shifted down with more board capacitance or shifted up with less board capacitance.

Not 100% tested.

### **Test and Measurement Set-up**

### **Voltage and Timing Definitions**

Figure 1. Duty Cycle Definition

Figure 2. ER =  $(0.6 \times V_{DD}) / t3$ , EF =  $(0.6 \times V_{DD}) / t4$

### **Ordering Information**

| Ordering Code   | Package Type               | Operating Range | Operating Voltage | Features                  |  |  |

|-----------------|----------------------------|-----------------|-------------------|---------------------------|--|--|

| Lead-free       |                            |                 |                   |                           |  |  |

| CY241V8ASXC-02  | 8-pin SOIC                 | Commercial      | 3.3V              | Linear VCXO control curve |  |  |

| CY241V8ASXC-02T | 8-pin SOIC – Tape and Reel | Commercial      | 3.3V              | Linear VCXO control curve |  |  |

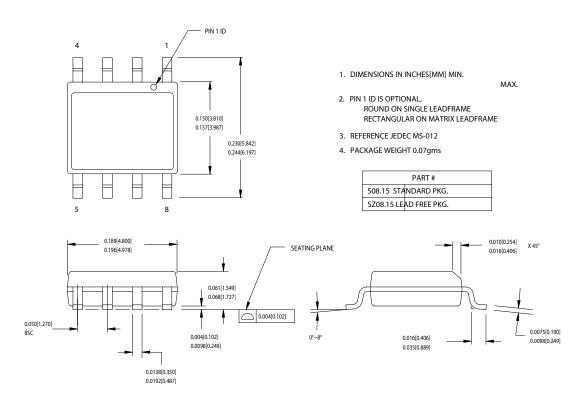

#### **Package Drawing and Dimensions**

#### 8-lead (150-Mil) SOIC S8

51-85066-\*C

All product or company names mentioned in this document may be the trademarks of their respective holders.

# **Document History Page**

| Document Title: CY241V08A-02 MPEG Clock Generator with VCXO Document Number: 38-07674 |         |            |                    |                       |  |  |  |

|---------------------------------------------------------------------------------------|---------|------------|--------------------|-----------------------|--|--|--|

| REV.                                                                                  | ECN NO. | Issue Date | Orig. of<br>Change | Description of Change |  |  |  |

| **                                                                                    | 222320  | See ECN    | RGL                | New Data Sheet        |  |  |  |

| *A                                                                                    | 338335  | See ECN    | RGL                | Added Lead-free       |  |  |  |