#

## **Data Sheet**

SPI interface with error detection

error detection

Vss to VDD analog signal range

compatible

Includes CRC, invalid read/write address, and SCLK count

Guaranteed break-before-make switching allowing external wiring of switches to deliver multiplexer configurations

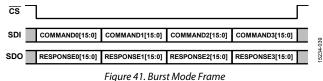

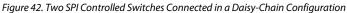

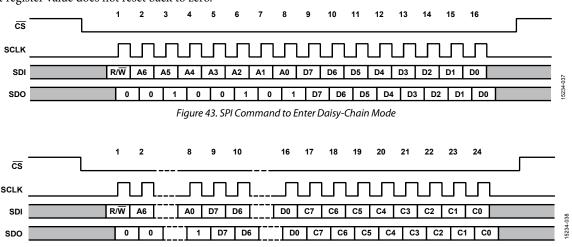

Supports burst mode and daisy-chain mode Industry standard SPI Mode 0 and Mode 3 interface

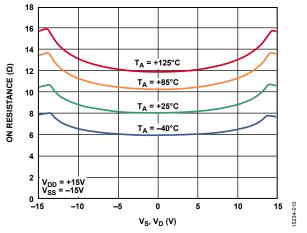

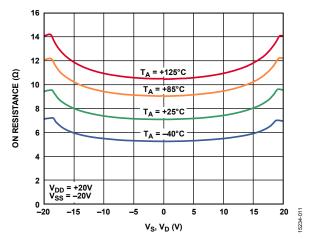

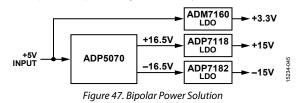

Fully specified at  $\pm 15$  V,  $\pm 20$  V,  $\pm 12$  V, and  $\pm 36$  V

±9 V to ±22 V dual-supply operation

9 V to 40 V single-supply operation Latch-up proof analog switch pins

1.8 V logic compatibility with 2.7 V  $\leq$  V<sub>L</sub>  $\leq$  3.3 V

**FEATURES**

# ADGS5412

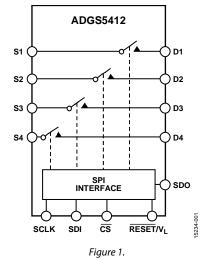

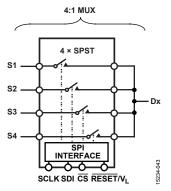

## FUNCTIONAL BLOCK DIAGRAM

APPLICATIONS

Low on resistance (<10  $\Omega$ )

8 kV HBM ESD rating

Relay replacement Automatic test equipment Data acquisition Instrumentation Avionics Audio and video switching Communication systems

## **GENERAL DESCRIPTION**

The ADGS5412 contains four independent single-pole/singlethrow (SPST) switches. A serial peripheral interface (SPI) controls the switches. The SPI interface has robust error detection features, including cyclic redundancy check (CRC) error detection, invalid read/write address detection, and serial clock (SCLK) count error detection.

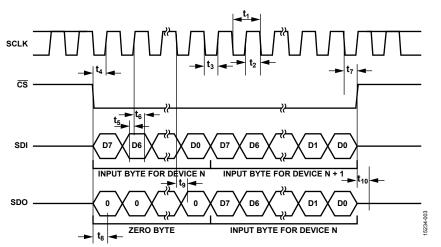

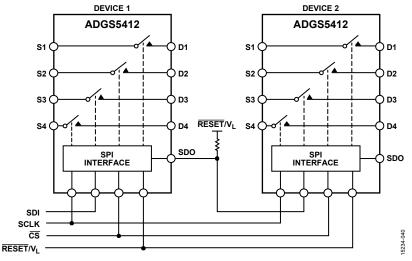

It is possible to daisy-chain multiple ADGS5412 devices together, which enables the configuration of multiple devices with a minimal amount of digital lines. The ADGS5412 can also operate in burst mode to decrease the time between SPI commands.

Each switch conducts equally well in both directions when on, and each switch has an input signal range that extends to the supplies. In the off condition, signal levels up to the supplies are blocked.

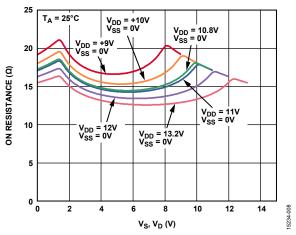

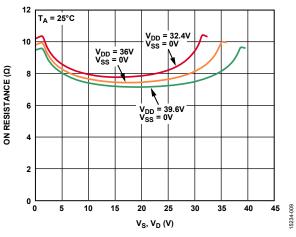

The on-resistance profile is very flat over the full analog input range, which ensures good linearity and low distortion when switching audio signals. The ADGS5412 exhibits break-before-

Rev. 0 Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. make switching action, allowing use of the device in multiplexer applications with external wiring.

## **PRODUCT HIGHLIGHTS**

- SPI interface removes the need for parallel conversion and logic traces and reduces general-purpose input/output (GPIO) channel count.

- 2. Daisy-chain mode removes additional logic traces when multiple devices are used.

- 3. CRC, invalid read/write address, and SCLK count error detection ensure a robust digital interface.

- 4. CRC error detection capabilities allow for the use of the ADGS5412 in safety critical systems.

- 5. Guaranteed break-before-make switching allows the use of the ADGS5412 in multiplexer configurations with external wiring.

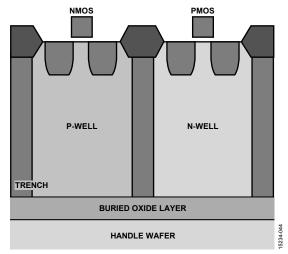

- Trench isolation analog switch section guards against latch-up. A dielectric trench separates the positive (P) and negative (N) channel transistors thereby preventing latch-up even under severe overvoltage conditions.

# **TABLE OF CONTENTS**

| Features 1                                     |

|------------------------------------------------|

| Applications1                                  |

| Functional Block Diagram1                      |

| General Description1                           |

| Product Highlights 1                           |

| Revision History 2                             |

| Specifications                                 |

| ±15 V Dual Supply 3                            |

| ±20 V Dual Supply 5                            |

| 12 V Single Supply7                            |

| 36 V Single Supply9                            |

| Continuous Current per Channel, Sx or Dx11     |

| Timing Characteristics11                       |

| Absolute Maximum Ratings13                     |

| ESD Caution13                                  |

| Pin Configurations and Function Descriptions14 |

| Typical Performance Characteristics            |

| Test Circuits                                  |

| Terminology                                    |

| Theory of Operation                            |

| Address Mode 22                                |

| Error Detection Features                       |

## Break-Before-Make Switching......25 Digital Input Buffers ...... 25 Register Summary ...... 27

#### **REVISION HISTORY**

5/2017—Revision 0: Initial Version

# **SPECIFICATIONS**

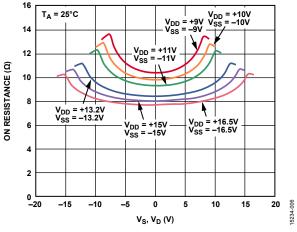

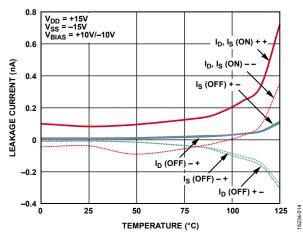

## ±15 V DUAL SUPPLY

Positive supply ( $V_{DD}$ ) = 15 V ± 10%, negative supply ( $V_{SS}$ ) = -15 V ± 10%, digital supply ( $V_L$ ) = 2.7 V to 5.5 V, GND = 0 V, unless otherwise noted.

| Parameter                                                    | +25°C | –40°C to +85°C | -40°C to +125°C                    | Unit   | Test Conditions/Comments                                            |

|--------------------------------------------------------------|-------|----------------|------------------------------------|--------|---------------------------------------------------------------------|

| ANALOG SWITCH                                                |       |                |                                    |        |                                                                     |

| Analog Signal Range                                          |       |                | V <sub>DD</sub> to V <sub>SS</sub> | v      |                                                                     |

| On Resistance, R <sub>on</sub>                               | 9.8   |                |                                    | Ωtyp   | $V_s = \pm 10 V$ , $I_s = -10 mA$ ;<br>see Figure 29                |

|                                                              | 11    | 14             | 16                                 | Ωmax   | $V_{DD} = +13.5 V, V_{SS} = -13.5 V$                                |

| On-Resistance Match Between Channels, $\Delta R_{\text{ON}}$ | 0.35  |                |                                    | Ωtyp   | $V_s = \pm 10 V$ , $I_s = -10 mA$                                   |

|                                                              | 0.7   | 0.9            | 1.1                                | Ωmax   |                                                                     |

| On-Resistance Flatness, R <sub>FLAT (ON)</sub>               | 1.2   |                |                                    | Ωtyp   | $V_s = \pm 10 V$ , $I_s = -10 mA$                                   |

|                                                              | 1.6   | 2              | 2.2                                | Ωmax   |                                                                     |

| LEAKAGE CURRENTS                                             |       |                |                                    |        | $V_{DD} = +16.5 V, V_{SS} = -16.5 V$                                |

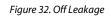

| Source Off Leakage, Is (Off)                                 | ±0.05 |                |                                    | nA typ | $V_s = \pm 10 \text{ V}, V_D = \mp 10 \text{ V};$<br>see Figure 32  |

|                                                              | ±0.25 | ±0.75          | ±3.5                               | nA max |                                                                     |

| Drain Off Leakage, $I_D$ (Off)                               | ±0.05 |                |                                    | nA typ | $V_{S} = \pm 10 \text{ V}, V_{D} = \mp 10 \text{ V};$ see Figure 32 |

|                                                              | ±0.25 | ±0.75          | ±3.5                               | nA max |                                                                     |

| Channel On Leakage, I <sub>D</sub> (On), I <sub>s</sub> (On) | ±0.1  |                |                                    | nA typ | $V_s = V_D = \pm 10 V$ ; see Figure 28                              |

|                                                              | ±0.4  | ±2             | ±12                                | nA max |                                                                     |

| DIGITAL OUTPUT                                               |       |                |                                    |        |                                                                     |

| Output Voltage                                               |       |                |                                    |        |                                                                     |

| Low, Vol                                                     |       |                | 0.4                                | V max  | I <sub>SINK</sub> = 5 mA                                            |

|                                                              |       |                | 0.2                                | V max  | I <sub>SINK</sub> = 1 mA                                            |

| High Impedance Leakage Current                               | 0.001 |                |                                    | μA typ | $V_{OUT} = V_{GND} \text{ or } V_L$                                 |

|                                                              |       |                | ±0.1                               | μA max |                                                                     |

| High Impedance Output Capacitance                            | 4     |                |                                    | pF typ |                                                                     |

| DIGITAL INPUTS                                               |       |                |                                    |        |                                                                     |

| Input Voltage                                                |       |                |                                    |        |                                                                     |

| High, V <sub>INH</sub>                                       |       |                | 2                                  | V min  | $3.3 V < V_L \le 5.5 V$                                             |

|                                                              |       |                | 1.35                               | V min  | $2.7~V \leq V_L \leq 3.3~V$                                         |

| Low, V <sub>INL</sub>                                        |       |                | 0.8                                | V max  | $3.3 V < V_L \le 5.5 V$                                             |

|                                                              |       |                | 0.8                                | V max  | $2.7~V \leq V_L \leq 3.3~V$                                         |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>          | 0.002 |                |                                    | μA typ | $V_{IN} = V_{GND} \text{ or } V_L$                                  |

|                                                              |       |                | ±0.1                               | μA max |                                                                     |

| Digital Input Capacitance, C <sub>IN</sub>                   | 4     |                |                                    | pF typ |                                                                     |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                         |       |                |                                    |        |                                                                     |

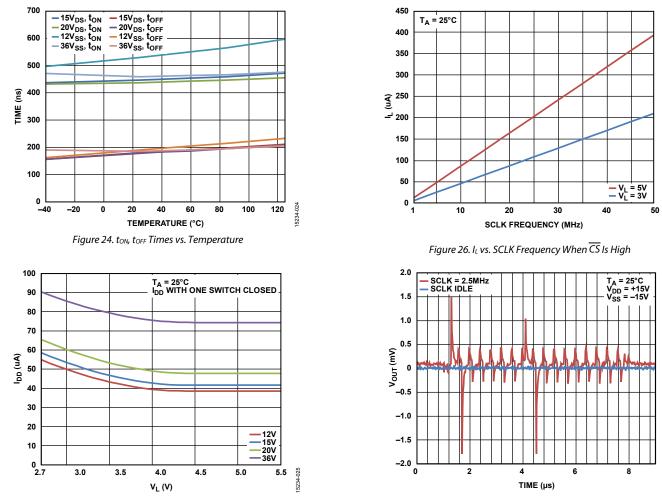

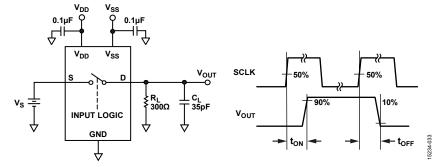

| ton                                                          | 460   |                |                                    | ns typ | $R_L = 300 \Omega, C_L = 35 pF$                                     |

|                                                              | 540   | 560            | 580                                | ns max | $V_s = 10 V$ ; see Figure 36                                        |

| toff                                                         | 185   |                |                                    | ns typ | $R_L = 300 \Omega$ , $C_L = 35 pF$                                  |

|                                                              | 225   | 240            | 270                                | ns max | $V_s = 10 V$ ; see Figure 36                                        |

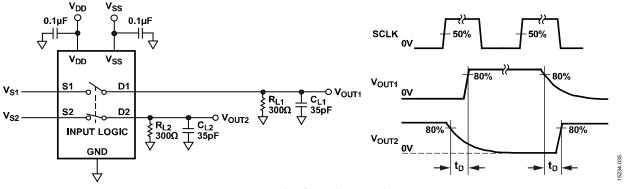

| Break-Before-Make Time Delay, t <sub>D</sub>                 | 245   |                |                                    | ns typ | $R_L = 300 \Omega$ , $C_L = 35 pF$                                  |

|                                                              |       |                | 195                                | ns min | $V_{s1} = V_{s2} = 10 V$ , see Figure 35                            |

| Parameter                                           | +25°C | –40°C to +85°C | -40°C to +125°C | Unit        | <b>Test Conditions/Comments</b>                                            |

|-----------------------------------------------------|-------|----------------|-----------------|-------------|----------------------------------------------------------------------------|

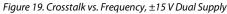

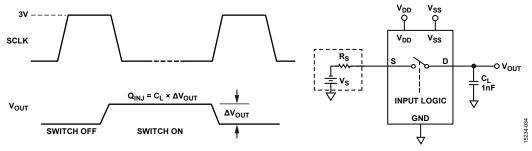

| Charge Injection, Q <sub>INJ</sub>                  | 245   |                |                 | pC typ      | $V_s = 0 V$ , $R_s = 0 \Omega$ , $C_L = 1 nF$ ;<br>see Figure 37           |

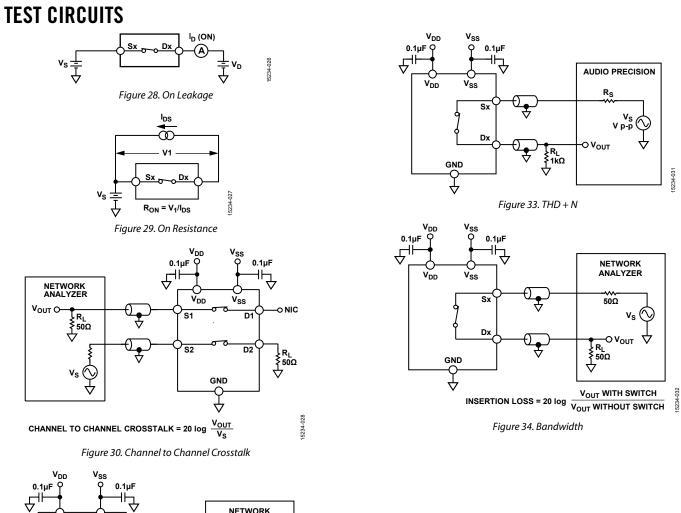

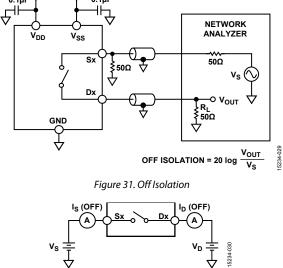

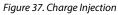

| Off Isolation                                       | -78   |                |                 | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , f = 100 kHz; see Figure 31              |

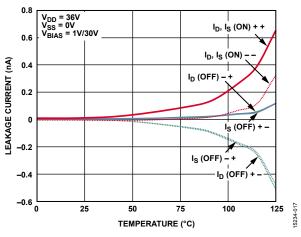

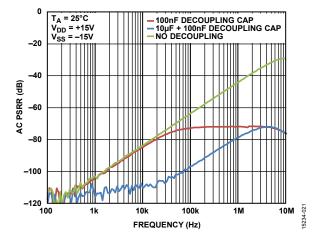

| Channel to Channel Crosstalk                        | -70   |                |                 | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;<br>see Figure 30          |

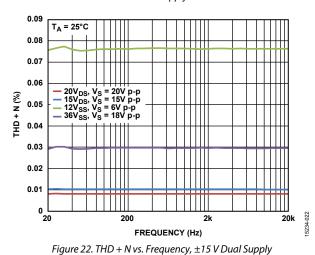

| Total Harmonic Distortion + Noise,<br>THD + N       | 0.01  |                |                 | % typ       | $R_L = 1 \text{ k}\Omega$ , 15 V p-p, f = 20 Hz to 20 kHz; see Figure 33   |

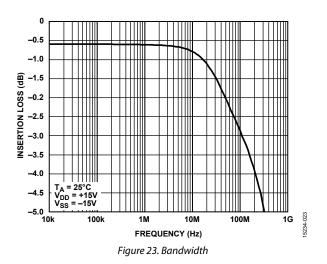

| –3 dB Bandwidth                                     | 167   |                |                 | MHz typ     | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 34                           |

| Insertion Loss                                      | -0.7  |                |                 | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;<br>see Figure 34          |

| Off Switch Source Capacitance, C <sub>s</sub> (Off) | 18    |                |                 | pF typ      | $V_{s} = 0 V, f = 1 MHz$                                                   |

| Off Switch Drain Capacitance, $C_D$ (Off)           | 18    |                |                 | pF typ      | $V_{s} = 0 V, f = 1 MHz$                                                   |

| On Switch Capacitance, $C_D$ (On), $C_S$ (On)       | 57    |                |                 | pF typ      | $V_{s} = 0 V, f = 1 MHz$                                                   |

| POWER REQUIREMENTS                                  | 1     |                |                 |             | $V_{DD} = +16.5 \text{ V}, \text{ V}_{SS} = -16.5 \text{ V}$               |

| Positive Supply Current, IDD                        | 45    |                |                 | μA typ      | Digital inputs = $0 \text{ V or } V_L$                                     |

|                                                     | 55    |                | 70              | μA max      |                                                                            |

|                                                     | 45    |                |                 | µA typ      | All switches closed,<br>$V_L = 5.5 V$                                      |

|                                                     | 110   |                |                 | μA typ      | All switches closed, $V_L = 2.7 V$                                         |

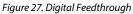

| Digital Supply Current, I∟                          |       |                |                 |             |                                                                            |

| Inactive                                            | 6.3   |                |                 | μA typ      | Digital inputs = $0 V \text{ or } V_{L}$                                   |

|                                                     |       |                | 8.0             | µA max      | 2 .                                                                        |

| Inactive, SCLK = 1 MHz                              | 14    |                |                 | μA typ      | $\overline{CS} = V_L$ and SDI = 0 V or $V_L$ ,<br>$V_L = 5 V$              |

|                                                     | 7     |                |                 | μA typ      | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 3 V$            |

| SCLK = 50 MHz                                       | 390   |                |                 | µA typ      | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ , $V_L = 5 V$               |

|                                                     | 210   |                |                 | μA typ      | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 3 V$            |

| Inactive, SDI = 1 MHz                               | 15    |                |                 | μA typ      | $\overline{CS}$ and SCLK = 0 V or V <sub>L</sub> ,<br>V <sub>L</sub> = 5 V |

|                                                     | 7.5   |                |                 | μA typ      | $\overline{CS}$ and SCLK = 0 V or V <sub>L</sub> ,<br>V <sub>L</sub> = 3 V |

| SDI = 25 MHz                                        | 230   |                |                 | μA typ      | $\overline{CS}$ and SCLK = 0 V or V <sub>L</sub> ,<br>V <sub>L</sub> = 5 V |

|                                                     | 120   |                |                 | µA typ      | $\overline{CS}$ and SCLK = 0 V or V <sub>L</sub> ,<br>V <sub>L</sub> = 3 V |

| Active at 50 MHz                                    | 1.8   |                |                 | mA typ      | Digital inputs toggle between 0 V and $V_L$ , $V_L = 5.5 V$                |

|                                                     |       |                | 2.1             | mA max      |                                                                            |

|                                                     | 0.7   |                |                 | mA typ      | Digital inputs toggle between 0 V and $V_L$ , $V_L = 2.7 V$                |

|                                                     |       |                | 1.0             | mA max      |                                                                            |

| Negative Supply Current, Iss                        | 0.001 |                |                 | μA typ      | Digital inputs = $0 \text{ V}$ or $V_{L}$                                  |

|                                                     |       |                | 1.0             | µA max      |                                                                            |

| V <sub>DD</sub> /V <sub>SS</sub>                    |       |                | ±9/±22          | V min/V max | GND = 0V                                                                   |

<sup>1</sup> Guaranteed by design; not subject to production test.

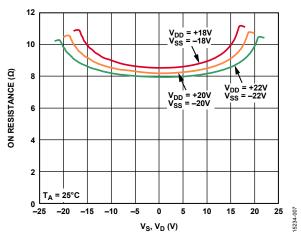

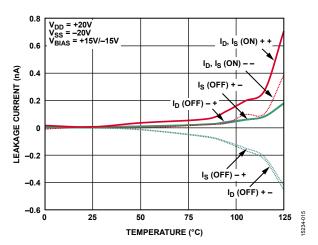

### ±20 V DUAL SUPPLY

$V_{\text{DD}}$  = 20 V  $\pm$  10%,  $V_{\text{SS}}$  = –20 V  $\pm$  10%,  $V_{\text{L}}$  = 2.7 V to 5.5 V, GND = 0 V, unless otherwise noted.

| Parameter                                                    | +25°C | –40°C to +85°C | –40°C to +125°C                    | Unit   | Test Conditions/Comments                                                   |

|--------------------------------------------------------------|-------|----------------|------------------------------------|--------|----------------------------------------------------------------------------|

| ANALOG SWITCH                                                |       |                |                                    |        |                                                                            |

| Analog Signal Range                                          |       |                | V <sub>DD</sub> to V <sub>SS</sub> | V      |                                                                            |

| On Resistance, R <sub>ON</sub>                               | 9     |                |                                    | Ωtyp   | $V_s = \pm 15 V$ , $I_s = -10 mA$ ; see Figure 29                          |

|                                                              | 10    | 13             | 15                                 | Ωmax   | $V_{DD} = +18 V$ , $V_{SS} = -18 V$                                        |

| On-Resistance Match Between Channels, $\Delta R_{ON}$        | 0.35  |                |                                    | Ωtyp   | $V_s = \pm 15 V$ , $I_s = -10 mA$                                          |

|                                                              | 0.7   | 0.9            | 1.1                                | Ωmax   |                                                                            |

| On-Resistance Flatness, R <sub>FLAT (ON)</sub>               | 1.6   |                |                                    | Ωtyp   | $V_s = \pm 15 V$ , $I_s = -10 mA$                                          |

|                                                              | 1.9   | 2.3            | 2.7                                | Ωmax   |                                                                            |

| LEAKAGE CURRENTS                                             |       |                |                                    |        | $V_{DD} = +22 V, V_{SS} = -22 V$                                           |

| Source Off Leakage, $I_s$ (Off)                              | ±0.05 |                |                                    | nA typ | $V_{S}$ = ±15 V, $V_{D}$ = $\mp$ 15 V; see Figure 32                       |

|                                                              | ±0.25 | ±0.75          | ±3.5                               | nA max |                                                                            |

| Drain Off Leakage, $I_D$ (Off)                               | ±0.05 |                |                                    | nA typ | $V_s = \pm 15 \text{ V}, V_D = \mp 15 \text{ V}; \text{ see}$<br>Figure 32 |

|                                                              | ±0.25 | ±0.75          | ±3.5                               | nA max |                                                                            |

| Channel On Leakage, I <sub>D</sub> (On), I <sub>S</sub> (On) | ±0.1  |                |                                    | nA typ | $V_{s} = V_{D} = \pm 15 V$ ; see Figure 28                                 |

|                                                              | ±0.4  | ±2             | ±12                                | nA max |                                                                            |

| DIGITAL OUTPUT                                               |       |                |                                    |        |                                                                            |

| Output Voltage                                               |       |                |                                    |        |                                                                            |

| Low, V <sub>OL</sub>                                         |       |                | 0.4                                | V max  | $I_{SINK} = 5 \text{ mA}$                                                  |

|                                                              |       |                | 0.2                                | V max  | $I_{SINK} = 1 \text{ mA}$                                                  |

| High Impedance Leakage Current                               | 0.001 |                |                                    | μA typ | $V_{OUT} = V_{GND} \text{ or } V_L$                                        |

|                                                              |       |                | ±0.1                               | µA max |                                                                            |

| High Impedance Output<br>Capacitance                         | 4     |                |                                    | pF typ |                                                                            |

| DIGITAL INPUTS                                               |       |                |                                    |        |                                                                            |

| Input Voltage                                                |       |                |                                    |        |                                                                            |

| High, V <sub>INH</sub>                                       |       |                | 2                                  | V min  | $3.3~V < V_L \leq 5.5~V$                                                   |

|                                                              |       |                | 1.35                               | V min  | $2.7~V \leq V_L \leq 3.3~V$                                                |

| Low, V <sub>INL</sub>                                        |       |                | 0.8                                | V max  | $3.3 \text{ V} < V_L \leq 5.5 \text{ V}$                                   |

|                                                              |       |                | 0.8                                | V max  | $2.7~V \leq V_L \leq 3.3~V$                                                |

| Input Current, IINL or IINH                                  | 0.002 |                |                                    | μA typ | $V_{IN} = V_{GND} \text{ or } V_L$                                         |

|                                                              |       |                | ±0.1                               | µA max |                                                                            |

| Digital Input Capacitance, C <sub>IN</sub>                   | 4     |                |                                    | pF typ |                                                                            |

| Parameter                                              | +25°C | –40°C to +85°C | -40°C to +125°C | Unit        | Test Conditions/Comments                                                              |

|--------------------------------------------------------|-------|----------------|-----------------|-------------|---------------------------------------------------------------------------------------|

| DYNAMIC CHARACTERISTICS <sup>1</sup>                   |       |                |                 |             |                                                                                       |

| t <sub>on</sub>                                        | 450   |                |                 | ns typ      | $R_L = 300 \Omega, C_L = 35 pF$                                                       |

|                                                        | 530   | 540            | 555             | ns max      | Vs = 10 V; see Figure 36                                                              |

| toff                                                   | 185   |                |                 | ns typ      | $R_{L} = 300 \Omega, C_{L} = 35 pF$                                                   |

|                                                        | 230   | 245            | 260             | ns max      | Vs = 10 V; see Figure 36                                                              |

| Break-Before-Make Time Delay, t <sub>D</sub>           | 235   |                |                 | ns typ      | $R_L = 300 \Omega, C_L = 35 pF$                                                       |

|                                                        |       |                | 185             | ns min      | $V_{s1} = V_{s2} = 10 V$ , see Figure 35                                              |

| Charge Injection, Q <sub>INJ</sub>                     | 310   |                |                 | pC typ      | $V_s = 0 V$ , $R_s = 0 \Omega$ , $C_L = 1 nF$ ; see Figure 37                         |

| Off Isolation                                          | -78   |                |                 | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 100 kHz$ ; see Figure 31                      |

| Channel-to-Channel Crosstalk                           | -70   |                |                 | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 30                        |

| Total Harmonic Distortion + Noise,<br>THD + N          | 0.008 |                |                 | % typ       | R∟ = 1 kΩ, 20 V p-p, f = 20 Hz to<br>20 kHz; see Figure 33                            |

| –3 dB Bandwidth                                        | 160   |                |                 | MHz typ     | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 34                                      |

| Insertion Loss                                         | -0.6  |                |                 | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 34                        |

| Off Switch Source Capacitance,<br>Cs (Off)             | 17    |                |                 | pF typ      | $V_s = 0 V$ , $f = 1 MHz$                                                             |

| Off Switch Drain Capacitance, $C_D$ (Off)              | 17    |                |                 | pF typ      | $V_s = 0 V$ , $f = 1 MHz$                                                             |

| On Switch Capacitance, C <sub>D</sub> (On),<br>Cs (On) | 56    |                |                 | pF typ      | $V_s = 0 V$ , $f = 1 MHz$                                                             |

| POWER REQUIREMENTS                                     |       |                |                 |             | $V_{DD} = +22 V, V_{SS} = -22 V$                                                      |

| Positive Supply Current, IDD                           | 50    |                |                 | μA typ      | Digital inputs = $0 V \text{ or } V_{L}$                                              |

|                                                        | 70    |                | 110             | μA max      |                                                                                       |

|                                                        | 50    |                |                 | μA typ      | All switches closed, $V_L = 5.5 V$                                                    |

|                                                        | 120   |                |                 | μA typ      | All switches closed, $V_L = 2.7 V$                                                    |

| l                                                      |       |                |                 |             |                                                                                       |

| Inactive                                               | 6.3   |                |                 | μA typ      | Digital inputs = $0 V \text{ or } V_{L}$                                              |

|                                                        |       |                | 8.0             | µA max      | _                                                                                     |

| Inactive, SCLK = 1 MHz                                 | 14    |                |                 | µA typ      | $\overline{CS} = V_L \text{ and } SDI = 0 \text{ V or } V_L,$<br>$V_L = 5 \text{ V}$  |

|                                                        | 7     |                |                 | µA typ      | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 3 V$                       |

| SCLK = 50 MHz                                          | 390   |                |                 | µA typ      | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 5 V$                       |

|                                                        | 210   |                |                 | µA typ      | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 3 V$                       |

| Inactive, SDI = 1 MHz                                  | 15    |                |                 | μA typ      | $\overline{\text{CS}}$ and $\text{SCLK} = 0 \text{ V}$ or $V_L$ , $V_L = 5 \text{ V}$ |

|                                                        | 7.5   |                |                 | μA typ      | $\overline{\text{CS}}$ and $\text{SCLK} = 0 \text{ V}$ or $V_L$ , $V_L = 3 \text{ V}$ |

| SDI = 25 MHz                                           | 230   |                |                 | μA typ      | $\overline{CS}$ and SCLK = 0 V or V <sub>L</sub> , V <sub>L</sub> = 5 V               |

|                                                        | 120   |                |                 | μA typ      | $\overline{\text{CS}}$ and SCLK = 0 V or V <sub>L</sub> , V <sub>L</sub> = 3 V        |

| Active at 50 MHz                                       | 1.8   |                |                 | mA typ      | Digital inputs toggle between $0 \text{ V}$ and $V_L$ , $V_L = 5.5 \text{ V}$         |

|                                                        |       |                | 2.1             | mA max      |                                                                                       |

|                                                        | 0.7   |                |                 | mA typ      | Digital inputs toggle between 0 V and $V_L$ , $V_L = 2.7$ V                           |

|                                                        |       |                | 1.0             | mA max      |                                                                                       |

| Negative Supply Current, Iss                           | 0.001 |                |                 | μA typ      | Digital inputs = $0 V \text{ or } V_{L}$                                              |

|                                                        |       |                | 1.0             | μA max      |                                                                                       |

| V <sub>DD</sub> /V <sub>ss</sub>                       |       |                | ±9/±22          | V min/V max | GND = 0V                                                                              |

<sup>1</sup> Guaranteed by design; not subject to production test.

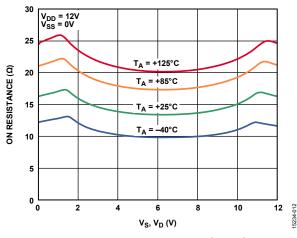

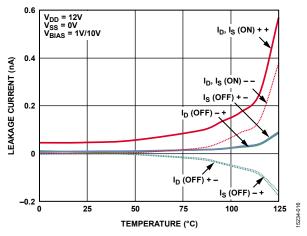

## **12 V SINGLE SUPPLY**

$V_{\text{DD}}$  = 12 V  $\pm$  10%,  $V_{\text{SS}}$  = 0 V,  $V_{\text{L}}$  = 2.7 V to 5.5 V, GND = 0 V, unless otherwise noted.

#### Table 3.

| Parameter                                                    | +25°C | –40°C to +85°C | -40°C to +125°C        | Unit   | Test Conditions/Comments                                           |

|--------------------------------------------------------------|-------|----------------|------------------------|--------|--------------------------------------------------------------------|

| ANALOG SWITCH                                                |       |                |                        |        |                                                                    |

| Analog Signal Range                                          |       |                | 0 V to V <sub>DD</sub> | V      |                                                                    |

| On-Resistance, Ron                                           | 19    |                |                        | Ωtyp   | $V_s = 0 V$ to 10 V, $I_s = -10 mA$ ;<br>see Figure 29             |

|                                                              | 22    | 27             | 31                     | Ωmax   | $V_{DD} = 10.8 V, V_{SS} = 0 V$                                    |

| On-Resistance Match Between Channels, $\Delta R_{\text{ON}}$ | 0.4   |                |                        | Ωtyp   | $V_{s} = 0 V$ to 10 V, $I_{s} = -10 \text{ mA}$                    |

|                                                              | 0.8   | 1              | 1.2                    | Ωmax   |                                                                    |

| On-Resistance Flatness, R <sub>FLAT (ON)</sub>               | 4.4   |                |                        | Ωtyp   | $V_{s} = 0 V$ to 10 V, $I_{s} = -10 \text{ mA}$                    |

|                                                              | 5.5   | 6.5            | 7.5                    | Ωmax   |                                                                    |

| LEAKAGE CURRENTS                                             |       |                |                        |        | $V_{DD} = 13.2 V, V_{SS} = 0 V$                                    |

| Source Off Leakage, Is (Off)                                 | ±0.05 |                |                        | nA typ | $V_s = 1 V/10 V$ , $V_D = 10 V/1 V$ ;<br>see Figure 32             |

|                                                              | ±0.25 | ±0.75          | ±3.5                   | nA max |                                                                    |

| Drain Off Leakage, I <sub>D</sub> (Off)                      | ±0.05 |                |                        | nA typ | $V_s = 1 V/10 V$ , $V_D = 10 V/1 V$ ;<br>see Figure 32             |

|                                                              | ±0.25 | ±0.75          | ±3.5                   | nA max |                                                                    |

| Channel On Leakage, $I_{\rm D}$ (On), $I_{\rm S}$ (On)       | ±0.1  |                |                        | nA typ | $V_s = V_D = 1 \text{ V}/10 \text{ V}$ ; see<br>Figure 28          |

|                                                              | ±0.4  | ±2             | ±12                    | nA max |                                                                    |

| DIGITAL OUTPUT                                               |       |                |                        |        |                                                                    |

| Output Voltage                                               |       |                |                        |        |                                                                    |

| Low, Vol                                                     |       |                | 0.4                    | V max  | $I_{SINK} = 5 \text{ mA}$                                          |

|                                                              |       |                | 0.2                    | V max  | $I_{SINK} = 1 \text{ mA}$                                          |

| High Impedance Leakage Current                               | 0.002 |                |                        | μA typ | $V_{OUT} = V_{GND} \text{ or } V_L$                                |

|                                                              |       |                | ±0.1                   | μA max |                                                                    |

| High Impedance Output Capacitance                            | 4     |                |                        | pF typ |                                                                    |

| DIGITAL INPUTS                                               |       |                |                        |        |                                                                    |

| Input Voltage                                                |       |                |                        |        |                                                                    |

| High, V <sub>INH</sub>                                       |       |                | 2                      | V min  | $3.3 V < V_L \le 5.5 V$                                            |

|                                                              |       |                | 1.35                   | V min  | $2.7~V \leq V_L \leq 3.3~V$                                        |

| Low, V <sub>INL</sub>                                        |       |                | 0.8                    | V max  | $3.3 V < V_L \le 5.5 V$                                            |

|                                                              |       |                | 0.8                    | V max  | $2.7~V \leq V_L \leq 3.3~V$                                        |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>          | 0.001 |                |                        | μA typ | $V_{IN} = V_{GND} \text{ or } V_L$                                 |

|                                                              |       |                | ±0.1                   | μA max |                                                                    |

| Digital Input Capacitance, C <sub>IN</sub>                   | 4     |                |                        | pF typ |                                                                    |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                         |       |                |                        | . ,.   |                                                                    |

| t <sub>oN</sub>                                              | 545   |                |                        | ns typ | $R_L = 300 \Omega, C_L = 35 pF$                                    |

|                                                              | 665   | 720            | 775                    | ns max | $V_s = 8 V$ ; see Figure 36                                        |

| t <sub>OFF</sub>                                             | 200   |                |                        | ns typ | $R_L = 300 \Omega, C_L = 35 pF$                                    |

|                                                              | 250   | 275            | 305                    | ns max | $V_s = 8 V$ ; see Figure 36                                        |

| Break-Before-Make Time Delay, t <sub>D</sub>                 | 320   |                | 2.00                   | ns typ | $R_L = 300 \Omega, C_L = 35 pF$                                    |

|                                                              |       |                | 235                    | ns min | $V_{s1} = V_{s2} = 8V$ , see Figure 35                             |

| Charge Injection, Q <sub>INJ</sub>                           | 105   |                | 200                    | pC typ | $V_s = 6 V, R_s = 0 \Omega, C_L = 1 nF;$<br>see Figure 37          |

| Off Isolation                                                | -78   |                |                        | dB typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ ,<br>f = 100  kHz; see Figure 31  |

| Channel-to-Channel Crosstalk                                 | -70   |                |                        | dB typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;<br>see Figure 30  |

| Total Harmonic Distortion + Noise,<br>THD + N                | 0.08  |                |                        | % typ  | $R_L = 1 k\Omega$ , 6 V p-p, f = 20 Hz<br>to 20 kHz; see Figure 33 |

| Parameter                                     | +25°C | –40°C to +85°C | –40°C to +125°C | Unit        | <b>Test Conditions/Comments</b>                                            |

|-----------------------------------------------|-------|----------------|-----------------|-------------|----------------------------------------------------------------------------|

| –3 dB Bandwidth                               | 180   |                |                 | MHz typ     | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 34                           |

| Insertion Loss                                | -1.3  |                |                 | dB typ      | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ;<br>see Figure 34          |

| Off Switch Source Capacitance, Cs (Off)       | 22    |                |                 | pF typ      | $V_{s} = 6 V, f = 1 MHz$                                                   |

| Off Switch Drain Capacitance, $C_D$ (Off)     | 22    |                |                 | pF typ      | $V_{s} = 6 V, f = 1 MHz$                                                   |

| On Switch Capacitance, $C_D$ (On), $C_S$ (On) | 56    |                |                 | pF typ      | $V_{s} = 6 V, f = 1 MHz$                                                   |

| POWER REQUIREMENTS                            |       |                |                 |             | $V_{DD} = 13.2 V$                                                          |

| Positive Supply Current, IDD                  | 40    |                |                 | μA typ      | Digital inputs = $0 V \text{ or } V_{L}$                                   |

|                                               |       |                | 65              | μA max      |                                                                            |

|                                               | 40    |                |                 | µA typ      | All switches closed, $V_L = 5.5 V$                                         |

|                                               | 105   |                |                 | µA typ      | All switches closed, $V_L = 2.7 V$                                         |

| l <sub>L</sub>                                |       |                |                 |             |                                                                            |

| Inactive                                      | 6.3   |                |                 | μA typ      | Digital inputs = 0 V or V <sub>L</sub>                                     |

|                                               |       |                | 8.0             | µA max      |                                                                            |

| Inactive, SCLK = 1 MHz                        | 14    |                |                 | μA typ      | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 5 V$            |

|                                               | 7     |                |                 | μA typ      | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 3 V$            |

| SCLK = 50 MHz                                 | 390   |                |                 | μA typ      | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 5 V$            |

|                                               | 210   |                |                 | μA typ      | $\overline{CS} = V_L$ and SDI = 0 V or $V_L$ ,<br>$V_L = 3 V$              |

| Inactive, SDI = 1 MHz                         | 15    |                |                 | μA typ      | $\overline{CS}$ and SCLK = 0 V or V <sub>L</sub> ,<br>V <sub>L</sub> = 5 V |

|                                               | 7.5   |                |                 | μA typ      | $\overline{CS}$ and SCLK = 0 V or V <sub>L</sub> ,<br>V <sub>L</sub> = 3 V |

| SDI = 25 MHz                                  | 230   |                |                 | μA typ      | $\overline{CS}$ and SCLK = 0 V or V <sub>L</sub> ,<br>V <sub>L</sub> = 5 V |

|                                               | 120   |                |                 | μA typ      | $\overline{CS}$ and SCLK = 0 V or V <sub>L</sub> ,<br>V <sub>L</sub> = 3 V |

| Active at 50 MHz                              | 1.8   |                |                 | mA typ      | Digital inputs toggle between 0 V and V <sub>L</sub> , $V_L = 5.5$ V       |

|                                               |       |                | 2.1             | mA max      |                                                                            |

|                                               | 0.7   |                |                 | mA typ      | Digital inputs toggle between 0 V and V <sub>L</sub> , $V_L = 2.7 V$       |

|                                               |       |                | 1.0             | mA max      |                                                                            |

| V <sub>DD</sub>                               |       |                | 9/40            | V min/V max | $GND = 0 V, V_{ss} = 0 V$                                                  |

<sup>1</sup> Guaranteed by design; not subject to production test.

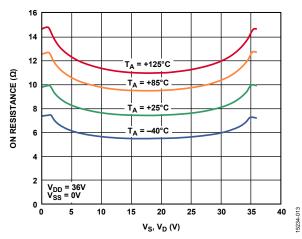

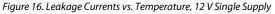

## **36 V SINGLE SUPPLY**

$V_{\text{DD}}$  = 36 V  $\pm$  10%,  $V_{\text{SS}}$  = 0 V,  $V_{\text{L}}$  = 2.7 V to 5.5 V, GND = 0 V, unless otherwise noted.

| Parameter                                                    | +25°C | –40°C to +85°C | -40°C to +125°C | Unit   | Test Conditions/Comments                                                                       |

|--------------------------------------------------------------|-------|----------------|-----------------|--------|------------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                                | 125 C | 10 0 10 10 0   | 40 0 0 1 125 0  | onic   |                                                                                                |

| Analog Signal Range                                          |       |                | 0 V to VDD      | v      |                                                                                                |

| On Resistance, R <sub>ON</sub>                               | 10.6  |                |                 | Ωtyp   | $V_s = 0 V$ to 30 V, $I_s = -10 mA$ ; see Figure 29                                            |

|                                                              | 12    | 15             | 17              | Ωmax   | $V_{DD} = 32.4 \text{ V}, \text{ V}_{SS} = 0 \text{ V}$                                        |

| On-Resistance Match Between<br>Channels, ΔR <sub>oN</sub>    | 0.35  |                |                 | Ωtyp   | $V_{\text{S}}$ = 0 V to 30 V, $I_{\text{S}}$ = $-10$ mA                                        |

|                                                              | 0.7   | 0.9            | 1.1             | Ωmax   |                                                                                                |

| On-Resistance Flatness, R <sub>FLAT(ON)</sub>                | 2.9   |                |                 | Ωtyp   | $V_s = 0 V$ to 30 V, $I_s = -10 mA$                                                            |

|                                                              | 3.4   | 4              | 4.7             | Ωmax   |                                                                                                |

| LEAKAGE CURRENTS                                             |       |                |                 |        | $V_{DD} = 39.6 V, V_{SS} = 0 V$                                                                |

| Source Off Leakage, $I_s$ (Off)                              | ±0.05 |                |                 | nA typ | $V_{s} = 1 \text{ V}/30 \text{ V}, V_{D} = 30 \text{ V}/1 \text{ V}; \text{ see}$<br>Figure 32 |

|                                                              | ±0.25 | ±0.75          | ±3.5            | nA max |                                                                                                |

| Drain Off Leakage, $I_D$ (Off)                               | ±0.05 |                |                 | nA typ | $V_{s} = 1 \text{ V}/30 \text{ V}, V_{D} = 30 \text{ V}/1 \text{ V}; \text{ see}$<br>Figure 32 |

|                                                              | ±0.25 | ±0.75          | ±3.5            | nA max |                                                                                                |

| Channel On Leakage, I <sub>D</sub> (On), I <sub>S</sub> (On) | ±0.1  |                |                 | nA typ | $V_{s} = V_{D} = 1 \text{ V}/30 \text{ V}$ ; see Figure 28                                     |

|                                                              | ±0.4  | ±2             | ±12             | nA max |                                                                                                |

| DIGITAL OUTPUT                                               |       |                |                 |        |                                                                                                |

| Output Voltage                                               |       |                |                 |        |                                                                                                |

| Low, V <sub>OL</sub>                                         |       |                | 0.4             | V max  | $I_{SINK} = 5 \text{ mA}$                                                                      |

|                                                              |       |                | 0.2             | V max  | $I_{SINK} = 1 \text{ mA}$                                                                      |

| High Impedance Leakage Current                               | 0.001 |                |                 | μA typ | $V_{OUT} = V_{GND} \text{ or } V_L$                                                            |

|                                                              |       |                | ±0.1            | μA max |                                                                                                |

| High Impedance Output<br>Capacitance                         | 4     |                |                 | pF typ |                                                                                                |

| DIGITAL INPUTS                                               |       |                |                 |        |                                                                                                |

| Input Voltage                                                |       |                |                 |        |                                                                                                |

| High, V <sub>INH</sub>                                       |       |                | 2               | V min  | $3.3 \text{ V} < \text{V}_{\text{L}} \leq 5.5 \text{ V}$                                       |

|                                                              |       |                | 1.35            | V min  | $2.7~V \leq V_L \leq 3.3~V$                                                                    |

| Low, V <sub>INL</sub>                                        |       |                | 0.8             | V max  | $3.3~V < V_L \leq 5.5~V$                                                                       |

|                                                              |       |                | 0.8             | V max  | $2.7~V \leq V_L \leq 3.3~V$                                                                    |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>          | 0.002 |                |                 | μA typ | $V_{IN} = V_{GND} \text{ or } V_L$                                                             |

|                                                              |       |                | ±0.1            | μA max |                                                                                                |

| Digital Input Capacitance, C <sub>IN</sub>                   | 4     |                |                 | pF typ |                                                                                                |

| Parameter                                              | +25°C | -40°C to +85°C | -40°C to +125°C | Unit             | <b>Test Conditions/Comments</b>                                                   |

|--------------------------------------------------------|-------|----------------|-----------------|------------------|-----------------------------------------------------------------------------------|

| DYNAMIC CHARACTERISTICS <sup>1</sup>                   |       |                |                 |                  |                                                                                   |

| t <sub>on</sub>                                        | 470   |                |                 | ns typ           | $R_L = 300 \Omega$ , $C_L = 35 pF$                                                |

|                                                        | 555   | 565            | 580             | ns max           | Vs = 18 V; see Figure 36                                                          |

| t <sub>OFF</sub>                                       | 195   |                |                 | ns typ           | $R_{L} = 300 \Omega, C_{L} = 35 pF$                                               |

|                                                        | 245   | 250            | 260             | ns max           | Vs = 18 V; see Figure 36                                                          |

| Break-Before-Make Time Delay, t <sub>D</sub>           | 245   |                |                 | ns typ           | $R_{L} = 300 \Omega, C_{L} = 35 pF$                                               |

|                                                        |       |                | 185             | ns min           | $V_{s1} = V_{s2} = 18 V$ , see Figure 35                                          |

| Charge Injection, Q <sub>INJ</sub>                     | 285   |                |                 | pC typ           | $V_s = 18 V$ , $R_s = 0 \Omega$ , $C_L = 1 nF$ ; see Figure 37                    |

| Off Isolation                                          | -78   |                |                 | dB typ           | $R_L = 50 \Omega$ , $C_L = 5 pF$ , f = 100 kHz; se<br>Figure 31                   |

| Channel-to-Channel Crosstalk                           | -70   |                |                 | dB typ           | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 30                    |

| Total Harmonic Distortion + Noise,<br>THD + N          | 0.03  |                |                 | % typ            | R∟ = 1 kΩ, 18 V p-p, f = 20 Hz to<br>20 kHz; see Figure 33                        |

| –3 dB Bandwidth                                        | 174   |                |                 | MHz typ          | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 3-                                  |

| Insertion Loss                                         | -0.7  |                |                 | dB typ           | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 1 MHz$ ; see Figure 34                    |

| Off Switch Source Capacitance,<br>C <sub>s</sub> (Off) | 17    |                |                 | pF typ           | $V_{s} = 18 V$ , f = 1 MHz                                                        |

| Off Switch Drain Capacitance, $C_D$ (Off)              | 17    |                |                 | pF typ           | $V_{s} = 18 V$ , f = 1 MHz                                                        |

| On Switch Capacitance, $C_D$ (On), $C_s$ (On)          | 55    |                |                 | pF typ           | $V_{s} = 18 V$ , f = 1 MHz                                                        |

| POWER REQUIREMENTS                                     |       |                |                 |                  | $V_{DD} = 39.6 V$                                                                 |

| Positive Supply Current, IDD                           | 80    |                |                 | μA typ           | Digital inputs = $0 V$ or $V_L$                                                   |

|                                                        | 100   |                | 130             | μA max           |                                                                                   |

|                                                        | 80    |                |                 | μA typ           | All switches closed, $V_L = 5.5 V$                                                |

| IL                                                     | 135   |                |                 | μA typ           | All switches closed, $V_L = 2.7 V$                                                |

| Inactive                                               | 6.3   |                |                 | μA typ           | Digital inputs = 0 V or V∟                                                        |

|                                                        | 0.0   |                | 8.0             | µA max           |                                                                                   |

| Inactive, SCLK = 1 MHz                                 | 14    |                |                 | µA typ           | $\overline{CS} = V_L$ and SDI = 0 V or $V_L$ ,<br>$V_L = 5 V$                     |

|                                                        | 7     |                |                 | μA typ           | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 3 V$                   |

| SCLK = 50 MHz                                          | 390   |                |                 | μA typ           | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 5 V$                   |

|                                                        | 210   |                |                 | μA typ           | $\overline{CS} = V_L$ and $SDI = 0 V$ or $V_L$ ,<br>$V_L = 3 V$                   |

| Inactive, SDI = 1 MHz                                  | 15    |                |                 | μA typ           | $\overline{CS}$ and SCLK = 0 V or V <sub>L</sub> , V <sub>L</sub> = 5 V           |

|                                                        | 7.5   |                |                 | μA typ           | $\overline{CS}$ and $SCLK = 0 V$ or $V_L, V_L = 3 V$                              |

| SDI = 25 MHz                                           | 230   |                |                 | μA typ           | $\overline{CS}$ and $SCLK = 0 V$ or $V_L, V_L = 5 V$                              |

|                                                        | 120   |                |                 | μΑ typ<br>μΑ typ | $\overline{\text{CS}}$ and $\text{SCLK} = 0 \text{ V or } V_L, V_L = 3 \text{ V}$ |

| Active at 50 MHz                                       | 120   |                |                 | mA typ           | Digital inputs toggle between $0 \text{ V}$ and $V_L$ , $V_L = 3 \text{ V}$       |

|                                                        |       |                | 2.1             | mA max           | 0 v anu v <sub>L</sub> , v <sub>L</sub> – 3.3 v                                   |

|                                                        | 0.7   |                | 2.1             | mA typ           | Digital inputs toggle between $0 \text{ V}$ and $V_L$ , $V_L = 2.7 \text{ V}$     |

|                                                        |       |                | 1.0             | mA max           |                                                                                   |

| V <sub>DD</sub>                                        |       |                | 9/40            | V min/V max      | $GND = 0 V, V_{ss} = 0 V$                                                         |

<sup>1</sup> Guaranteed by design; not subject to production test.

## CONTINUOUS CURRENT PER CHANNEL, S<sub>x</sub> OR D<sub>x</sub>

#### Table 5. Four Channels On

| 25°C | 85°C                            | 125°C                                        | Unit                                         |

|------|---------------------------------|----------------------------------------------|----------------------------------------------|

|      |                                 |                                              |                                              |

|      |                                 |                                              |                                              |

| 126  | 94                              | 59                                           | mA max                                       |

|      |                                 |                                              |                                              |

| 133  | 98                              | 63                                           | mA max                                       |

|      |                                 |                                              |                                              |

| 97   | 71                              | 44                                           | mA max                                       |

|      |                                 |                                              |                                              |

| 131  | 97                              | 62                                           | mA max                                       |

|      |                                 |                                              |                                              |

| 25°C | 85°C                            | 125°C                                        | Unit                                         |

|      |                                 |                                              |                                              |

|      |                                 |                                              |                                              |

| 220  |                                 |                                              |                                              |

| 230  | 154                             | 102                                          | mA max                                       |

| 230  | 154                             | 102                                          | mA max                                       |

| 230  | 154<br>160                      | 102<br>104                                   | mA max<br>mA max                             |

|      |                                 |                                              |                                              |

|      |                                 |                                              |                                              |

|      | 133<br>97<br>131<br><b>25°C</b> | 126 94   133 98   97 71   131 97   25°C 85°C | 126 94 59   133 98 63   97 71 44   131 97 62 |

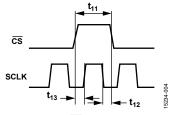

#### TIMING CHARACTERISTICS

LFCSP ( $\theta_{JA} = 50^{\circ}C/W$ )

$V_L$  = 2.7 V to 5.5 V; GND = 0 V; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Guaranteed by design and characterization, not production tested.

239

158

104

mA max

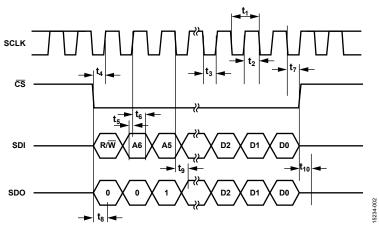

| Table 7.                    |                                              |        |                                                 |

|-----------------------------|----------------------------------------------|--------|-------------------------------------------------|

| Parameter                   | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Test Conditions/Comments                        |

| t <sub>1</sub>              | 20                                           | ns min | SCLK period                                     |

| t <sub>2</sub>              | 8                                            | ns min | SCLK high pulse width                           |

| t <sub>3</sub>              | 8                                            | ns min | SCLK low pulse width                            |

| t <sub>4</sub>              | 10                                           | ns min | CS falling edge to SCLK rising edge             |

| t <sub>5</sub>              | 6                                            | ns min | Data setup time                                 |

| t <sub>6</sub>              | 8                                            | ns min | Data hold time                                  |

| t7                          | 10                                           | ns min | SCLK rising edge to $\overline{CS}$ rising edge |

| t <sub>8</sub>              | 20                                           | ns max | CS falling edge to SDO data available           |

| t <sub>9</sub> <sup>1</sup> | 20                                           | ns max | SCLK falling edge to SDO data available         |

| t <sub>10</sub>             | 20                                           | ns max | CS rising edge to SDO returns to high impedance |

| t11                         | 20                                           | ns min | CS high time between SPI commands               |

| t <sub>12</sub>             | 8                                            | ns min | CS falling edge to SCLK becomes stable          |

| t <sub>13</sub>             | 8                                            | ns min | CS rising edge to SCLK becomes stable           |

<sup>1</sup> Measured with the 1 k $\Omega$  pull-up resistor to V<sub>L</sub> and 20 pF load. The parameter t<sub>9</sub> determines the maximum SCLK frequency when SDO is used.

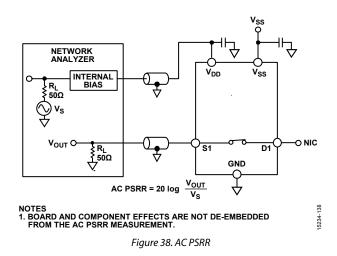

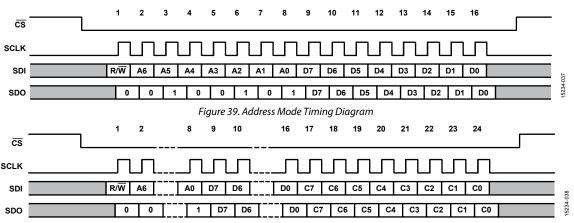

Figure 2. Addressable Mode Timing Diagram

Figure 4. SCLK/CS Timing Relationship

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 8.

| Parameter                                                        | Rating                                                                                 |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| V <sub>DD</sub> to V <sub>SS</sub>                               | 48 V                                                                                   |

| V <sub>DD</sub> to GND                                           | –0.3 V to +48 V                                                                        |

| Vss to GND                                                       | +0.3 V to -48 V                                                                        |

| V <sub>L</sub> to GND                                            | –0.3 V to +6 V                                                                         |

| Analog Inputs <sup>1</sup>                                       | V <sub>ss</sub> – 0.3 V to V <sub>DD</sub> + 0.3 V or<br>30 mA, whichever occurs first |

| Digital Inputs <sup>1</sup>                                      | –0.3 V to +6 V                                                                         |

| Peak Current, $S_X$ or $D_X$                                     | 261 mA (pulsed at 1 ms, 10%<br>duty cycle maximum)                                     |

| Continuous Current, S <sub>x</sub> or D <sub>x<sup>2</sup></sub> | Data + 15%                                                                             |

| Temperature Ranges                                               |                                                                                        |

| Operating                                                        | -40°C to +125°C                                                                        |

| Storage                                                          | –65°C to +150°C                                                                        |

| Junction Temperature                                             | 150°C                                                                                  |

| Thermal Impedance, θ <sub>JA</sub>                               | 50°C/W                                                                                 |

| Reflow Soldering Peak<br>Temperature, Pb Free                    | 260 (+0/-5)°C                                                                          |

| Human Body Model (HBM) ESD<br>Rating                             | 8 kV                                                                                   |

$^{\rm 1}$  Overvoltages at the  $S_{\rm X}$  pins and  $D_{\rm X}$  pins are clamped by internal diodes. Limit the current to the maximum ratings given.

<sup>2</sup> See Table 5.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Only one absolute maximum rating can be applied at any one time.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

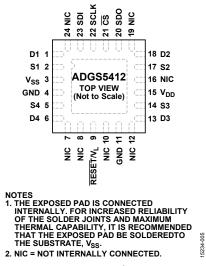

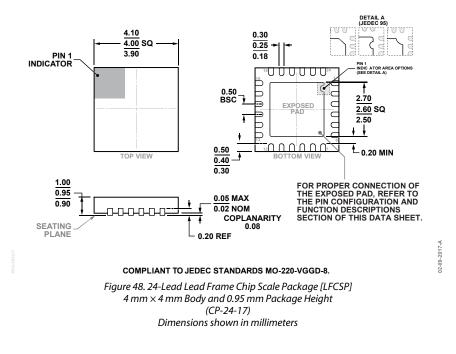

# **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

Figure 5. Pin Configuration

#### **Table 9. Pin Function Descriptions**

| Pin No.           | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1                 | D1              | Drain Terminal 1. This pin can be an input or an output.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 2                 | S1              | Source Terminal 1. This pin can be an input or an output.                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 3                 | Vss             | Most Negative Power Supply Potential. In single-supply applications, tie this pin to GND.                                                                                                                                                                                                                                      |  |  |  |  |  |

| 4, 11             | GND             | Ground (0 V) Reference.                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 5                 | S4              | Source Terminal 4. This pin can be an input or an output.                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 6                 | D4              | Drain Terminal 4. This pin can be an input or an output.                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 7, 8, 10,         | NIC             | Not Internally Connected.                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |