### Linear Current Regulator and Controller for Automotive LED Arrays

#### FEATURES AND BENEFITS

- Six LED current sinks rated up to 60 mA (A6274) or 120 mA (A6284)

- Total LED drive current—up to 360 mA or 720 mA

- Wide input voltage range of 5 to 42 V for start/stop, coldcrank, and load-dump requirements

- Low-dropout voltage—drives two series WLEDs from 7 V input

- Gate driver for external ballast P-MOSFET

- LEDs combined in two groups with separate ENx and ISETx

- LED current level set by external reference resistors

- Internal or external PWM dimming

- Controlled output drivers slew during PWM for lower EMI

- Fault detection features: LED string open, LED pin short-to-ground, single LED short, VOUT short-to-ground, VIN overvoltage, and thermal protection

- Input supply and temperature-based derating

- Automotive K-temperature range (-40°C to 150°C)

#### PACKAGES:

20-Pin eTSSOP (LP) with Exposed Thermal Pad AEC-Q100 qualified

#### DESCRIPTION

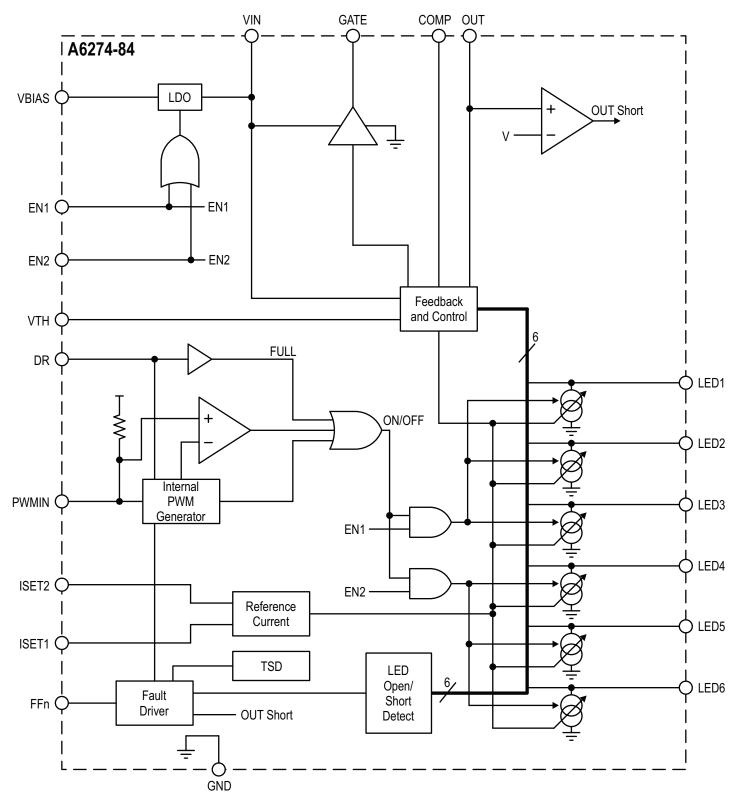

The A6274 and A6284 are programmable linear current regulator ICs for driving automotive LED arrays. The LED current is programmed by external resistors. These devices sink up to 60 mA (A6274) or 120 mA (A6284), from each of six LED pins, to drive strings of high-brightness LEDs. LED pins can be paralleled to drive even higher current LED strings. Current settings are typically accurate to 2%, while typical matching between LED strings is 0.8%.

LED light output can be adjusted by PWM dimming. The ICs provide an internal PWM dimming circuit that is programmed by external resistors for PWM frequency and duty cycle. It can also accept an external PWM signal. Multiple ICs can be configured in parallel for larger lighting systems. An internal FULL ( $V_{DR} > 3.6 V$ ) option is provided to override the PWM-dimming ratio for full LED current.

LED current derating with temperature and programmable VIN levels allows operation over a wide range of operating conditions.

Continued on next page ...

#### **APPLICATIONS**

- Automotive rear combination light

- DRL/position

- General automotive lighting

### Linear Current Regulator and Controller for Automotive LED Arrays

#### **DESCRIPTION** (continued)

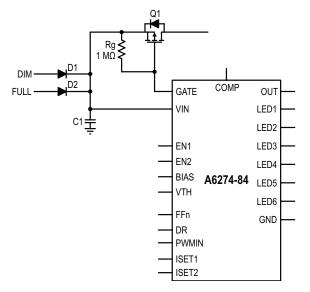

A GATE pin is provided to drive an external P-channel MOSFET, which serves as an active ballast resistor to reduce the heat dissipation within the IC package. It also serves as an input disconnect switch in the event of an LED string short-to-ground fault.

The A6274 and A6284 provide a non-latching option while the A6274-1 and A6284-1 provide a latching option.

### SPECIFICATIONS

#### SELECTION GUIDE

| Part Number    | I <sub>LED(MAX)</sub> | FAULT Response<br>(see Table 2 for details) | Package                        | Packing <sup>1</sup>         |  |

|----------------|-----------------------|---------------------------------------------|--------------------------------|------------------------------|--|

| A6274KLPTR-T   | 60 mA per channel     | Unlatched MODE0                             |                                |                              |  |

| A6284KLPTR-T   | 120 mA per channel    | Unlatched MODE0                             | 20-pin eTSSOP with thermal pad |                              |  |

| A6274KLPTR-1-T | 60 mA per channel     | Latched MODE1                               | 20-pin erssop with thermal pad | 4,000 pieces per 13-in. reel |  |

| A6284KLPTR-1-T | 120 mA per channel    | Latched MODE1                               |                                |                              |  |

<sup>1</sup> Contact Allegro<sup>™</sup> for additional packing options.

#### ABSOLUTE MAXIMUM RATINGS<sup>3</sup>

| Characteristic                    | Symbol                                                                                                                                  | Notes                                                                                                                            | Rating                                        | Unit |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------|

| VIN, OUT, DR, EN1, EN2, COMP, FFn | V <sub>IN</sub> , V <sub>OUT</sub> ,<br>V <sub>COMP</sub> , V <sub>DR</sub> ,<br>V <sub>EN1</sub> , V <sub>EN2</sub> , V <sub>FFn</sub> |                                                                                                                                  | −0.3 to 45                                    | V    |

| GATE                              | V <sub>GATE</sub>                                                                                                                       |                                                                                                                                  | Max of (–0.3 or<br>V <sub>IN</sub> – 9) to 45 | V    |

| LED1 to LED6                      | V <sub>LEDx</sub>                                                                                                                       |                                                                                                                                  | -0.5 to 45                                    | V    |

| All other pins                    |                                                                                                                                         |                                                                                                                                  | -0.3 to 6.5                                   | V    |

| Junction Temperature              | TJ                                                                                                                                      |                                                                                                                                  | -40 to 150                                    | °C   |

| Transient Junction Temperature    | T <sub>Jt</sub>                                                                                                                         | Overtemperature event not exceeding 10 seconds, lifetime duration not exceeding 10 hours, determined by design characterization. | 175                                           | °C   |

| Storage Temperature Range         | T <sub>stg</sub>                                                                                                                        |                                                                                                                                  | -55 to 150                                    | °C   |

<sup>3</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

| Characteristic                         | Symbol           | Test Conditions <sup>4</sup>                      | Value | Unit |

|----------------------------------------|------------------|---------------------------------------------------|-------|------|

| Junction-to-Ambient Thermal Resistance | R <sub>θJA</sub> | Estimated, on 4-layer PCB based on JEDEC standard | 29    | °C/W |

<sup>4</sup> Additional thermal information available on the Allegro website.

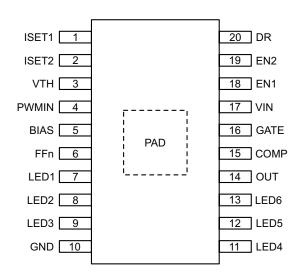

### PINOUT DIAGRAM AND TERMINAL LIST TABLE

**Terminal List Table**

#### Package LP, 20-Pin eTSSOP Pinout Diagram

| Number     | Symbol | Function                                                                                                                                                                                                                    |

|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | ISET1  | Sets LEDx sink current for LED1-3. Connect<br>resistor to GND to set current, up to 60 mA<br>(A6274) or 120 mA (A6284) per channel.                                                                                         |

| 2          | ISET2  | Sets LEDx sink current for LED4-6. Connect<br>resistor to GND to set current, up to 60 mA<br>(A6274) or 120 mA (A6284) per channel.<br>Connect ISET2 to BIAS if only one resistor<br>setting is required for LED1-6.        |

| 3          | VTH    | Sets input voltage threshold for current foldback and $V_{OUT}$ threshold for open-LED fault (D, E, F, and G) disable threshold.                                                                                            |

| 4          | PWMIN  | PWM frequency setting. Internal PWM frequency<br>set when connected to GND through a resistor<br>and uses external PWM when a logic signal is<br>applied to this pin.                                                       |

| 5          | BIAS   | Output of internal bias regulator. Connect a 1 $\mu$ F decoupling capacitor near to IC pin. BIAS pin can deliver up to 7 mA to an external load.                                                                            |

| 6          | FFn    | Active-low fault flag. This pin can be used as<br>an input pin while using "-1" latching version. If<br>pulled low, IC will turn all LEDs off for one-out-<br>all-out functionality across multiple chips in the<br>system. |

| 7, 8, 9    | LED1-3 | Three LED current sinks. Connect the cathode of each LED string to these pins.                                                                                                                                              |

| 10         | GND    | Ground pin.                                                                                                                                                                                                                 |

| 11, 12, 13 | LED4-6 | Three LED current sinks. Connect the cathode of each LED string to these pins.                                                                                                                                              |

| 14         | OUT    | Connect to drain of series-pass MOSFET.                                                                                                                                                                                     |

| 15         | COMP   | Connect a 470 nF capacitor across COMP pin<br>and drain node of external PMOS. If PMOS is<br>not used, connect this pin to VIN.                                                                                             |

| 16         | GATE   | Gate drive for series-pass MOSFET. If PMOS is not used, connect this pin to VIN.                                                                                                                                            |

| 17         | VIN    | Input voltage to IC. Connect to source of series-<br>pass P-channel MOSFET. Connect a decoupling<br>capacitor close to this pin.                                                                                            |

| 18         | EN1    | Active-high-enable input for LED1-3.                                                                                                                                                                                        |

| 19         | EN2    | Active-high-enable input for LED4-6.                                                                                                                                                                                        |

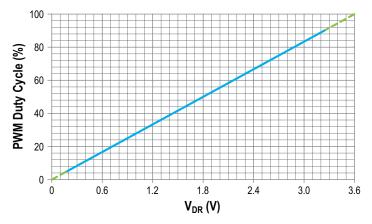

| 20         | DR     | Voltage on this pin sets dimming duty cycle<br>when $0 < V_{DR} < 3.6$ V. IC operates with 100%<br>duty cycle in internal and external PWM mode<br>when $V_{DR} > V_{DRDC}$ (max)                                           |

| _          | PAD    | Thermal pad. Solder to ground plane for better thermal performance.                                                                                                                                                         |

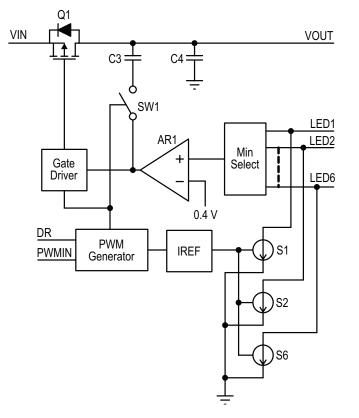

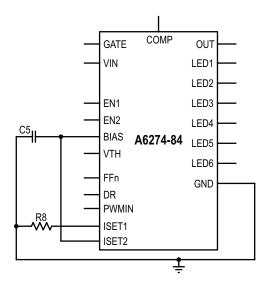

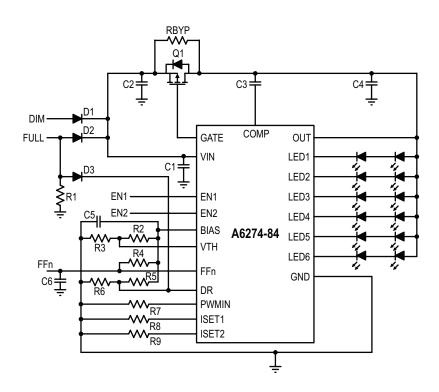

Functional Block Diagram

### Linear Current Regulator and Controller for Automotive LED Arrays

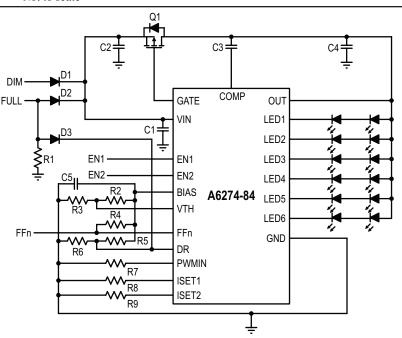

# **ELECTRICAL CHARACTERISTICS**: Valid at $V_{IN}$ = 14 V, $V_{ENx}$ = 3.3 V; • indicates specifications across the full operating temperature range with $T_J$ = -40°C to 150°C; other specifications are at $T_J$ = 25°C, unless noted otherwise. Refer to Figure 1 for typical application circuit.

| Characteristics                                       | Symbol                     | Test Conditions                                                                                                                   |   | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---|------|------|------|------|

| INPUT SPECIFICATIONS                                  |                            | ·                                                                                                                                 |   |      |      |      |      |

| Operating Input Voltage Range                         | V <sub>IN</sub>            |                                                                                                                                   | • | 5    | _    | 42   | V    |

| Input Quiescent Current <sup>1</sup>                  | Ι <sub>Q</sub>             | V <sub>ENx</sub> = high, FULL mode                                                                                                |   | _    | -    | 6    | mA   |

| Input Sleep Supply Current <sup>1</sup>               | I <sub>QSLEEP</sub>        | $V_{EN1} = V_{EN2} = 0 V; V_{DR} = V_{BIAS}$                                                                                      | • | _    | -    | 6    | μA   |

| INTERNAL BIAS CIRCUIT                                 |                            |                                                                                                                                   |   |      |      |      |      |

| BIAS Pin Voltage                                      | V <sub>BIAS</sub>          | $I_{\rm BIAS}$ = 0 to 7 mA, 5.6 V $\leq$ V_{\rm IN} $\leq$ 18 V                                                                   | • | 4.75 | 5    | 5.25 | V    |

| BIAS Pin Dropout                                      | V <sub>BIASDROP</sub>      | Minimum voltage drop across VIN and BIAS pins. $I_{\rm BIAS}$ < 7 mA, $\rm V_{\rm IN}$ = 5 V                                      |   | _    | 0.3  | -    | V    |

| V <sub>BIAS</sub> Undervoltage Release Threshold      | VBIASSTART                 | V <sub>IN</sub> rising                                                                                                            | • | -    | -    | 4.6  | V    |

| V <sub>BIAS</sub> Undervoltage Lockout Stop Threshold | VBIASSTOP                  | V <sub>IN</sub> falling                                                                                                           | • | -    | -    | 4.2  | V    |

| P-CHANNEL MOSFET DRIVER SPECIFICAT                    | ION                        |                                                                                                                                   |   |      |      |      |      |

| GATE Sink Current <sup>1</sup>                        |                            | Due to on-chip current limit, 10 V < V_{IN} < 18 V                                                                                |   | 4    | -    | -    | mA   |

| GATE SINK CUTENL'                                     | GATE(SINK)                 | Due to on-chip current limit, $V_{IN}$ = 5 V                                                                                      |   | 2    | -    | -    | mA   |

| GATE Maximum Voltage (w.r.t. V <sub>IN</sub> )        | V <sub>GATE(MAX)</sub>     | $V_{IN} - V_{GATE}, V_{LEDx} = 0.3 V$                                                                                             |   | 8    | 10   | 12   | V    |

| GATE Minimum Voltage (w.r.t. V <sub>IN</sub> )        | V <sub>GATE(MIN)</sub>     | $V_{IN} - V_{GATE}, V_{LEDx} = 1 V$                                                                                               |   | -    | 130  | 360  | mV   |

| PMOS Detect Threshold                                 | V <sub>GATE(PMOS)</sub>    | Voltage measured ( $V_{IN} - V_{GATE}$ ) at end of startup to detect PMOS connected                                               |   | _    | 600  | _    | mV   |

| LEDx CURRENT DRIVER SPECIFICATION                     | <u>^</u>                   | ·                                                                                                                                 |   |      |      |      |      |

| LEDy Decyletics Valtage 23                            |                            | A6274; not in derating                                                                                                            | • | -    | 0.4  | 0.7  | V    |

| LEDx Regulation Voltage <sup>2a</sup>                 | V <sub>LEDreg</sub>        | A6284; not in derating                                                                                                            | • | -    | 0.55 | 0.85 | V    |

| LEDx Accuracy <sup>3</sup>                            | Err <sub>LEDx</sub>        | Measured at I <sub>LED(MAX)</sub> , LEDx mismatch < 0.5 V, 5 V < V <sub>IN</sub> < 18 V, T <sub>J</sub> = 0°C to 150°C            |   | _    | 2    | 3.5  | %    |

| LEDx Matching <sup>4</sup>                            | $\Delta I_{LEDx}$          | ISET2 connected to BIAS; compared to average $I_{LEDx}$ , measured at $I_{LED(MAX)}$ , LEDx mismatch < 1 V, 5 V < $V_{IN}$ < 18 V | • | _    | 0.8  | 3    | %    |

|                                                       |                            | A6274                                                                                                                             | • | _    | 60   | _    | mA   |

| Maximum LEDx Current                                  | I <sub>LED(MAX)</sub>      | A6284                                                                                                                             | • | _    | 120  | -    | mA   |

| Minimum I EDv Oversent                                |                            | A6274                                                                                                                             |   | -    | 6    | -    | mA   |

| Minimum LEDx Current                                  | I <sub>LED(MIN)</sub>      | A6284                                                                                                                             |   | -    | 12   | -    | mA   |

| Maximum LED Current, ISETx Pin Short-to-              |                            | A6274                                                                                                                             |   | -    | 66   | -    | mA   |

| Ground <sup>2</sup>                                   | I <sub>LED(ISETshrt)</sub> | A6284                                                                                                                             |   | _    | 129  | _    | mA   |

| LED Current Ramp Time                                 | t <sub>RAMP</sub>          | I <sub>LEDx</sub> 10% to 90% and 90% to 10%                                                                                       |   | _    | 8    | _    | μs   |

|                                                       |                            | A6274                                                                                                                             |   | _    | 248  | _    | A/A  |

| ISETx to ILEDx Gain                                   | <b>9</b> ILED              | A6284                                                                                                                             |   | _    | 492  | _    | A/A  |

| ISETx Voltage Level                                   | V <sub>ISET</sub>          | 0.015 mA ≤ I <sub>ISETx</sub> ≤ 0.3 mA                                                                                            |   | _    | 1.2  | _    | V    |

Continued on the next page ...

## Linear Current Regulator and Controller for Automotive LED Arrays

#### ELECTRICAL CHARACTERISTICS (continued): Valid at V<sub>IN</sub> = 14 V, V<sub>ENx</sub> = 3.3 V; • indicates specifications across the full operating temperature range with T<sub>1</sub> = -40°C to 150°C; other specifications are at T<sub>1</sub> = 25°C, unless noted otherwise. Refer to Figure 1 for typical application circuit.

| Characteristics                                                                | Characteristics Symbol Test Conditions |                                                                                                                        |   | Min. | Тур.                 | Max. | Unit |  |

|--------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------|---|------|----------------------|------|------|--|

| PROTECTION                                                                     |                                        | •                                                                                                                      |   |      |                      |      |      |  |

| V <sub>IN</sub> Required to Derate I <sub>LED</sub> by 10%                     | V <sub>INth(L)</sub>                   | V <sub>VTH</sub> = 1.84 V                                                                                              |   | 19   | 20                   | 21   | V    |  |

| V <sub>IN</sub> Derating Range (V <sub>INth(L)</sub> to V <sub>INth(H)</sub> ) | V <sub>INthd</sub>                     | I <sub>LED</sub> drops from 90% to 50% level                                                                           |   | _    | 6.4                  | _    | V    |  |

| MOSFET Drain Short Protection Threshold                                        | V <sub>OUT(SC)</sub>                   | Measure across OUT and GND pins                                                                                        |   | _    | 1                    | _    | V    |  |

| MOSFET Drain Short Protection Blank Delay                                      | t <sub>d(OUT,scblnk)</sub>             | Protection disabled from enable instance                                                                               |   | _    | 1                    | _    | ms   |  |

| String Short Detect Voltage                                                    | V <sub>SC(STRING)</sub>                | While LED sinks are in regulation; sensed from VLEDx to VLEDreg, 5 V < $V_{IN}$ < 18 V                                 |   | 1.8  | -                    | 2.6  | V    |  |

| LEDx Not-In-Use Voltage                                                        | V <sub>LEDx(NULL)</sub>                | Detect during t <sub>LEDdet</sub> time period                                                                          |   | 0.18 | 0.26                 | 0.34 | V    |  |

| LEDx Pin Source Current                                                        | ILEDsrc                                | Source current for Not-In-Use Detection                                                                                |   | 65   | -                    | 95   | μA   |  |

| LED Connected Detect Time                                                      | t <sub>LEDdet</sub>                    | ENx = high and $V_{GATE} \le (V_{IN} - 3.3)$ at startup                                                                |   | _    | 5                    | _    | ms   |  |

| LEDx Short-to-Ground Detect Voltage                                            | V <sub>LED(SC)</sub>                   |                                                                                                                        |   | -    | -                    | 0.16 | V    |  |

| Open-LED Disable Voltage                                                       | V <sub>OLED_dis</sub>                  | Measured at OUT pin, V <sub>VTH</sub> = 2 V                                                                            |   | _    | 10                   | _    | V    |  |

| Input Overvoltage Threshold                                                    | V <sub>VINOV</sub>                     | $V_{EN1} = V_{EN2} = high$                                                                                             |   | _    | 43                   | _    | V    |  |

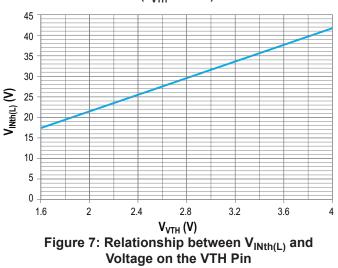

| Thermal Monitor Activation Temperature <sup>2</sup>                            | T <sub>JM</sub>                        | $T_J$ where $I_{LED}$ drops to 90% level                                                                               |   | _    | T <sub>JF</sub> – 21 | _    | °C   |  |

| Thermal Monitor Low-Current Temperature <sup>2</sup>                           | T <sub>JL</sub>                        | $T_J$ where $I_{LED}$ drops to 35% level                                                                               |   | _    | T <sub>JF</sub> – 7  | _    | °C   |  |

| Overtemperature Shutdown <sup>2</sup>                                          | T <sub>JF</sub>                        | Temperature increasing                                                                                                 |   | -    | 175                  | -    | °C   |  |

| Overtemperature Hysteresis <sup>2</sup>                                        | T <sub>J(HYS)</sub>                    | Recovery = $T_{JF} - T_{J(HYS)}$                                                                                       |   | -    | 30                   | -    | °C   |  |

| PWM DIMMING: INTERNAL AND EXTERNAL                                             |                                        |                                                                                                                        | · |      | · · · · · ·          |      |      |  |

| Internal-to-External PWM Mode Delay                                            | t <sub>d(PWM,INEX)</sub>               |                                                                                                                        |   | -    | 1                    | -    | μs   |  |

| External-to-Internal PWM Mode Delay                                            | t <sub>d(PWM,EXIN)</sub>               | $V_{PWMIN} < V_{LOGIC(L)}$                                                                                             |   | -    | 20                   | -    | ms   |  |

| PWM DIMMING INTERNAL                                                           | 'e                                     |                                                                                                                        |   |      | · · · · · ·          |      |      |  |

| Maximum PWM-Dimming Frequency                                                  | f <sub>PWM(MAX)</sub>                  | 7.15 k $\Omega$ between PWMIN and GND                                                                                  |   | -    | 2050                 | -    | Hz   |  |

| Minimum PWM-Dimming Frequency                                                  | f <sub>PWM(MIN)</sub>                  | 71.5 k $\Omega$ between PWMIN and GND                                                                                  |   | 195  | 215                  | 235  | Hz   |  |

|                                                                                | D <sub>PWM5</sub> <sup>2</sup>         | DR driven by resistor divider from BIAS,<br>V <sub>BIAS</sub> $\div$ V <sub>DR</sub> = 27.78, PWM = 205 Hz to<br>2 kHz | • | 4.5  | 5.0                  | 5.5  | %    |  |

| PWM Duty Cycle                                                                 | D <sub>PWM90</sub>                     | DR driven by resistor divider from BIAS,<br>$V_{BIAS} \div V_{DR}$ = 1.54, PWM = 205 Hz to<br>2 kHz                    |   | 87   | 90                   | 93   | %    |  |

|                                                                                | V <sub>DRDC(MAX)</sub>                 | Minimum required voltage on DR for 100% duty cycle                                                                     |   | 3.6  | -                    | -    | V    |  |

| DR Pin Current <sup>1</sup>                                                    | I <sub>DR(SRC)</sub>                   | $V_{DR} = 2 V$                                                                                                         |   | -    | -                    | 1    | μA   |  |

Continued on the next page ...

### Linear Current Regulator and Controller for Automotive LED Arrays

### ELECTRICAL CHARACTERISTICS (continued): Valid at V<sub>IN</sub> = 14 V, V<sub>ENx</sub> = 3.3 V; • indicates specifications across the full operating tempera-ture range with T<sub>1</sub> = -40°C to 150°C; other specifications are at T<sub>1</sub> = 25°C, unless noted otherwise. Refer to Figure 1 for typical application circuit.

| Characteristics                         | Symbol                    | Test Conditions                                              |   | Min. | Тур. | Max. | Unit |

|-----------------------------------------|---------------------------|--------------------------------------------------------------|---|------|------|------|------|

| LOGIC SIGNAL SPECIFICATIONS             |                           | ·                                                            |   |      |      |      |      |

| FFn Output (Open Drain)                 | V <sub>FFn(L)</sub>       | I <sub>FFn</sub> = 1 mA, fault asserted                      |   | _    | _    | 0.4  | V    |

| FFn Output Leakage Current <sup>1</sup> | I <sub>FFn(LKG)</sub>     | V <sub>FFn</sub> = 12 V, fault not asserted                  |   | -1   | -    | 1    | μA   |

| PWMIN, ENx Low Voltage                  | V <sub>LOGIC(L)</sub>     |                                                              | • | _    | -    | 0.8  | V    |

| PWMIN, ENx High Voltage                 | V <sub>LOGIC(H)</sub>     |                                                              | • | 2    | -    | _    | V    |

| FFn Input Low Voltage                   | V <sub>FFLOGIC(L)</sub>   | MODE = 1; FFn pin acts as bidirectional<br>pin when MODE = 1 | • | _    | -    | 0.8  | V    |

| FFn Input High Voltage                  | V <sub>FFLOGIC(H)</sub>   |                                                              | • | 2.1  | -    | _    | V    |

| PWMIN Input Hysteresis                  | V <sub>LOGIC(HYS)</sub>   |                                                              |   | 150  | 270  | _    | mV   |

| ENx Input Hysteresis                    | V <sub>LOGIC(HYS1)</sub>  |                                                              |   | 40   | -    | _    | mV   |

| ENx Internal Pull-Down Resistance       | R <sub>PD(ENx)</sub>      |                                                              |   | -    | 200  | -    | kΩ   |

| COMP SPECIFICATIONS                     |                           |                                                              |   |      |      |      |      |

| COMP Source Current                     | I <sub>COMP(SOURCE)</sub> |                                                              |   | -    | 320  | -    | μA   |

| COMP Sink Current <sup>2</sup>          | I <sub>COMP(SINK)</sub>   |                                                              |   | -    | -320 | -    | μA   |

| COMP Startup Sinking Current            | I <sub>COMP(START)</sub>  | V <sub>LEDx</sub> is < regulation voltage                    |   | -    | 2    | -    | mA   |

<sup>1</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), and positive current is defined as going into the node or pin (sinking).

<sup>2</sup> Ensured by design and characterization, not production tested.

<sup>2a</sup> Max limit ensured by design and characterization, not production tested.

3 LED accuracy is defined for A6274 as |[1 - (R<sub>ISETx</sub> × I<sub>LED(avg)</sub> ÷ 298)]] and for A6284 as |[1 - (R<sub>ISETx</sub> × I<sub>LED(avg)</sub> ÷ 590)]], where I<sub>LED(avg)</sub> is the average of I<sub>LED1</sub> through I<sub>LED6</sub>, R<sub>ISETx</sub> is in kΩ, and I<sub>LED</sub> is in mA.

4 LED current matching is defined as [(I<sub>LEDx</sub> - I<sub>LED(avg)</sub>) + I<sub>LED(avg)</sub>], with I<sub>LED(avg)</sub> as defined in Footnote 3.

### Linear Current Regulator and Controller for Automotive LED Arrays

### FUNCTIONAL DESCRIPTION

### **Powering Up**

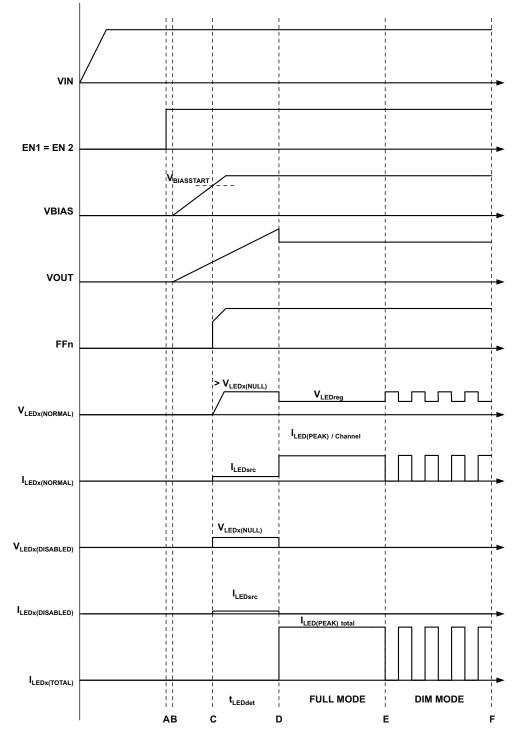

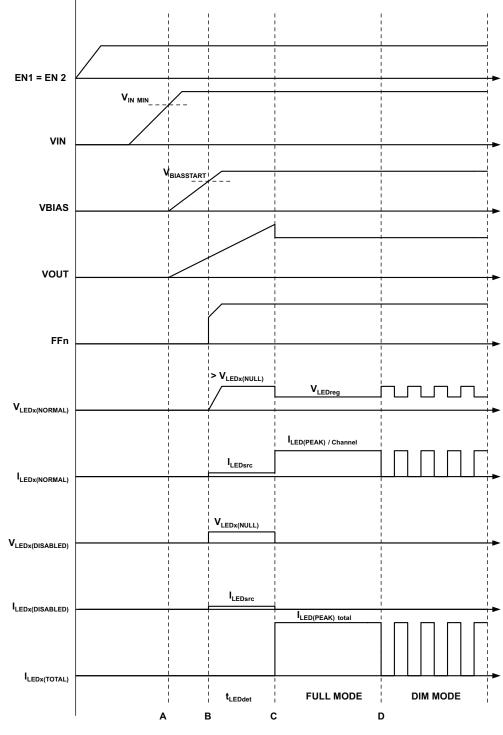

The A6274/84 can be enabled either by ENx inputs or by input voltage as shown in Figure 3 and 4 respectively. In both cases, the IC starts when the internal bias circuit voltage,  $V_{BIAS}$ , rises above its starting level,  $V_{BIASSTART}$ . Any existing latched fault is cleared.

The IC shuts down when input voltage or both ENx inputs fall such that the internal bias circuit voltage,  $V_{BIAS}$ , drops below its stopping level,  $V_{BIASSTOP}$ .

EN1 is the active-high-enable input for LED1-3 while EN2 is the active-high-enable input for LED4-6. To drive all the LED strings with common EN input, connect EN1 and EN2 together. EN1 and EN2 pins are high-voltage tolerant and can be directly connected to a power supply.

Refer to Figure 3 for startup with ENx. Once ENx goes high, the BIAS regulator is allowed to start after a few microseconds internal delay (A to B), and the IC powers up when  $V_{BIAS} > V_{BIASSTART}$  (at C). Once the IC powers up, it will check LEDx pin voltage to identify if any LEDx pin is used, unused, or shorted to ground.

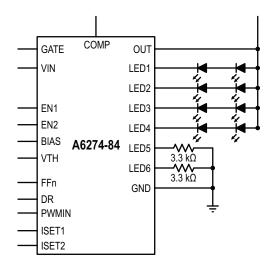

After startup, for the time period of  $t_{LEDdet}$  (C to D), the IC detects unused LED sink pins by injecting current  $I_{LEDsrc}$  to LEDx pins and measures voltage on the LEDx pins. If the LEDx voltage is equal to  $V_{LEDx(NULL)}$ , the IC detects it as an unused channel and disables the corresponding LEDx channel. The internal current source,  $I_{LEDsrc}$ , is removed after  $t_{LEDdet}$  time period and disabled strings will be removed from the regulation loop. The unused pin, with the pull-down resistor, will be taken out of regulation loop or fault detection. The FFn pin remains high during the  $t_{LEDdet}$  period. The enabled strings will be continuously monitored, and can be treated as a fault after the  $t_{LEDdet}$  period.

Table 1: LED Detection Voltage Thresholds

# Figure 2: Channel-select setup using LED1-4; LED5-6 unused. LED5-6 connected through 3.3 k $\Omega$ resistor to GND.

All unused pins must be connected with a resistor connected from LEDx to ground, as shown in Figure 2. LEDx pins source  $I_{LEDsrd}$  current. Voltage on an LEDx pin, when connected through resistor, will be  $V_{LEDx(NULL)}$ .

#### FULL and DIM Mode

When the DR pin voltage is above  $V_{DRDC(MAX)}$ , the LEDs operate with 100% duty cycle (FULL mode). In FULL mode, the LEDs turn on with 100% duty cycle regardless of internal or external PWM mode. When the DR pin voltage is lower than  $V_{DRDC(MAX)}$ , the LEDs operate with PWM dimming (DIM mode). PWM frequency and duty cycle in DIM mode is controlled by the PWMIN and DR pins.

| LED Pin Voltage Level                         | LED Pin                   | Action                                                                                                         |

|-----------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------|

| V <sub>LED(SC)</sub> (<160 mV)                | Indicates short-to-ground | FFn goes low after t <sub>LEDdet</sub> time period.                                                            |

| V <sub>LEDx(NULL)</sub><br>(>180 mV, <340 mV) | Not used                  | Unused LEDx is removed from regulation loop. Related sink remains disabled and latched until it is re-enabled. |

| V <sub>LEDx(NULL,max)</sub> (>400 mV)         | LED pin in use            | None                                                                                                           |

Figure 3: Typical Start Sequence with ENx

### Linear Current Regulator and Controller for Automotive LED Arrays

Figure 4: Typical Start Sequence with VIN

#### **PWM Dimming in DIM Mode**

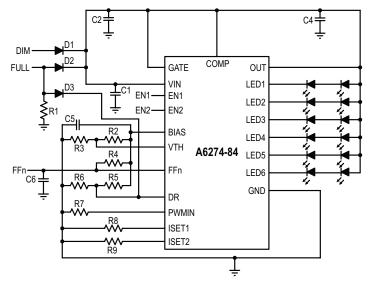

LED dimming during DIM mode can be controlled internally by the A6274/84, or externally. For external PWM mode, connect an external clock pulse on the PWMIN pin, which controls dimming, frequency, and duty cycle. The A6274/84 detects the logic level on the PWMIN pin. When logic voltage is applied on the PWMIN pin, the IC switches to external PWM mode where dimming, frequency, and duty cycle are directly controlled by signals on PWMIN pin.

In internal PWM mode, dimming frequency can be set using a resistor connected from PWMIN pin to GND as shown in Figure 1. It is not necessary to select the PWM mode before startup: the IC will transition from internal to external when PWMIN is raised above  $V_{LOGIC(H)}$ ; and it will transition from external to internal when external PWMIN signal is removed for more than 20 ms. LEDx will not blink; they will be off during this period.

The recommended range for PWM frequency is 200 Hz to 2 kHz. Maximum PWM frequency is limited due to acceptable error at minimum PWM duty cycle. At higher PWM frequency and smaller duty cycles, error in LED current increases due to slow ramp-up and ramp-down in LED current. It is recommended to use a minimum on-time > 20  $\mu$ s.

The equation for internal PWM frequency setting with the PWMIN pin resistor is given by:

$$f_{PWM} = (14165 \div R_{FPWM}) + 19$$

where  $f_{PWM}$  is in Hz and  $R_{FPWM}$  is in k $\Omega$ . For example, with a 29.4 k $\Omega$  resistor,  $f_{PWM} = 500$  Hz.

$R_{FPWM}$  must be greater than 5 k $\Omega$  for internal PWM; below this value, the PWMIN pin is detected at a logic-low level and operates in external PWM mode.

The voltage on the DR pin determines the operating duty cycle. For better accuracy, derive this voltage from BIAS using a voltage divider. The PWM duty cycle depends on the ratio of the DR and BIAS pin voltages. The duty cycle can be reduced, down to 5% (see Figure 5), as:

$$PWM(\%) = 139 \times V_{DR} \div V_{BLAS}$$

where  $V_{DR}$  and  $V_{BIAS}$  are in volts (V).

### **LED Current Setting**

The peak LED current can be set at up to 60 or 120 mA per channel through the ISETx pin. ISET1 sets current through LED1-3 and ISET2 sets current through LED4-6.

By connecting ISET2 to BIAS, ISET1 current can be mirrored on all enabled LED channels (LED1-6). This will improve current matching between LED1-6 when all LED strings are identical.

Connect a resistor,  $R_{ISETx}$ , between ISETx pin and ground, to set peak LED current through each channel. The value of peak LED current through each LEDx sink is given by:

$$I_{LED(PEAK)} = 298 \div R_{ISETx} (k\Omega) \quad \text{for A6274}$$

$$I_{LED(PEAK)} = 590 \div R_{ISETx} (k\Omega) \quad \text{for A6284}$$

where  $I_{LED}$  is in mA and  $R_{ISETx}$  in k $\Omega$ . This sets the peak current through each LEDx, referred as the 100% Current. The average LEDx current can be reduced from the 100% Current value by dimming PWM duty ratio.

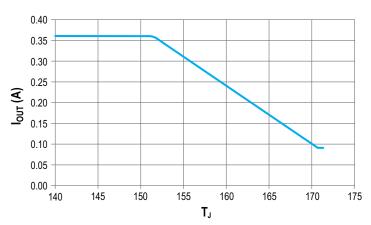

#### Input Overvoltage Derating

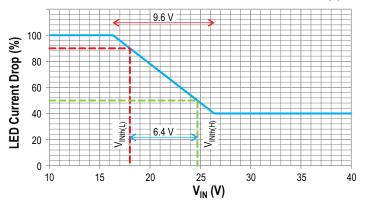

This feature takes effect at higher  $V_{IN}$  levels, limiting power dissipation in the IC and the external MOSFET. At higher input voltages, output current drops corresponding with increasing  $V_{IN}$ . Output current is controlled with peak current (see Figure 6). The  $V_{IN}$  threshold can be set with an external resistor divider connected from BIAS to VTH. The LED current drops to 90% at the  $V_{INth(L)}$  level and to 50% at  $V_{INth(H)}$  level. LED current further drops to 40% and stays at this level for higher input voltages. Voltage on VTH pin sets the  $V_{INth(L)}$  level, and the  $V_{INth(H)}$  level is typically higher than  $V_{INth(L)}$  by  $V_{INth}$  (6.4 V).

The recommended range for  $V_{INth(L)}$  is from 18 to 36 V.

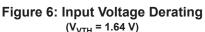

$$V_{INth(L)} = 10 \times V_{VTH} + 1.6$$

where  $V_{INth(L)}$  is the supply voltage level where LED current drops to the 90% level, and  $V_{VTH}$  is the voltage on VTH pin. Figure 7 shows relation between voltage on VTH pin and  $V_{INth(L)}$ .

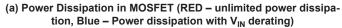

### **Thermal Derating and Protection Shutdown**

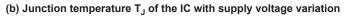

This feature takes effect at higher temperatures, limiting power dissipation in the IC and external MOSFETs. At higher temperatures, the LED current drops with increasing  $T_J$ , as shown in Figure 8. Thermal shutdown (TSD) completely disables the outputs under extreme overtemperature (>175°C) conditions, and FFn goes low. The IC restarts when the temperature drops by 30°C.

Figure 8: Output Current Foldback Based on Rising T<sub>J</sub> Output current changed by DC current control; when temperature exceeds 175°C (typ), the IC turns off due to TSD function, and turns on again at 145°C (30°C (typ)) hysteresis.

### **Operation of the Series-Pass Regulator**

The A6274/84 consists of six regulated and matched current sinks, and a series-pass regulator controller to minimize power dissipation in the sinks. The series-pass regulator is controlled such that all LEDx pin voltage is above regulation. LEDx pin having maximum forward voltage drop will be regulated by series-pass regulator. This ensures optimum voltage supplied to common-anode node of LED strings to drive all strings at the desired current.

A capacitor connected across COMP to the drain of the external MOSFET provides a pole for control-loop stability. It is recommended to use NTB5605 or NTD2955 as external PMOS.

When the external PMOS is not used, connect the GATE and COMP pins to VIN. When the PMOS pre-regulator is not used, the LED string short faults B and C will be disabled.

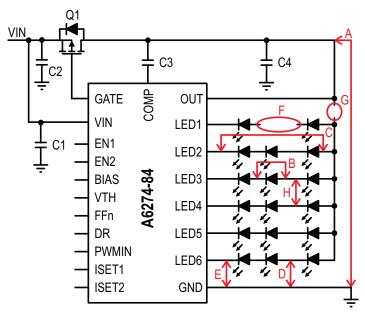

### Open-LED (FAULTs D, E, F, and G)

During normal operation, if the voltage on any enabled LED pin drops too low ( $V_{LEDx} < V_{LED(SC)}$ ) and  $V_{OUT}$  is greater than  $V_{OLED \ dis}$ , it may indicate either a short across LEDx and GND (Fault  $\overline{E}$ ), an open-LED (Fault F), a mid-LED-string short-to-ground (Fault D), or LED common-anode open (Fault G).

LEDs in faults D and E will only be reported on FF pin, but will not be protected, if MOSFET Q1 is not used.

### Short LED Faults (FAULTs B and C)

Short LED faults are detected while LED sinks are in regulation and  $V_{LEDx} - V_{LEDreg} > V_{SC}$  (STRING).

### **Open-LED Disable Threshold**

At power-up (EN1 or EN2 raised to logic high), if the input voltage is below  $V_{OLED\_dis}$ , faults D, E, F, and G will be disabled. Once  $V_{IN}$  is raised above  $V_{OLED\_dis}$ , the faults are enabled and will remain enabled unless  $V_{BIAS}$  drops below  $V_{BIASSTOP}$ . The IC will continue to operate normally in cases where these faults exist.  $V_{OLED\_dis}$  value is given by:

#### $V_{OLED\ dis} = 5 \times V_{VTH}$

Voltage on VTH pin sets the input voltage derating threshold  $(V_{INth(L)})$  as well as the open-LED disable level  $(V_{OLED\_dis})$ . Select the  $V_{VTH}$  voltage suitable to avoid an open-LED fault due to insufficient input voltage.

Figure 9: External MOSFET Regulator Loop

Figure 10: Various Faults Handled by A6274/84

#### **Table 2: Fault Description**

|      | Fault                             | Detection Criterion                                                                                                                                                     | -  | to-<br>tart | FFn    |                  | ED<br>nks        | MOS        | last<br>SFET<br>(1 |                                                                                                                                                                              | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------|--------|------------------|------------------|------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                   | MODE State $\rightarrow$                                                                                                                                                | 1  | 0           | 1 or 0 | 1                | 0                | 1          | 0                  | 1                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A    | MOSFET drain shorted to ground    | V <sub>OUT</sub> < V <sub>OUT(SC)</sub> . Fault<br>detected after 1 ms<br>blanking time from Q1<br>gate enabled.                                                        | N  | lo          | Low    | 1                | Гurn<br>)ff      | Turi       | n Off              | IC shutdown and                                                                                                                                                              | FFn pin goes low. This state remains latched until VIN or any<br>ENx toggled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Grou | up 1 Faults Based o               | n Maximum LEDx Pin Voltag                                                                                                                                               | ge |             |        |                  |                  |            |                    |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| В    | One LED short                     | While LED sinks are in<br>regulation. Sensed from<br>V <sub>LEDx</sub> to V <sub>LEDreg</sub> .<br>V <sub>LEDx</sub> – V <sub>LEDreg</sub> ><br>V <sub>SC(STRING)</sub> | No | Yes         | Low    | All Turn Off     | Operate Normally | Turn Off   | Operate Normally   | IC shutdown and<br>FFn pin goes<br>Iow. This state<br>remains latched<br>until VIN or any<br>ENx toggled.                                                                    | LEDx pin voltage on faulty string increases and IC detects<br>the fault. IC responds only by pulling FFn pin low as long<br>as fault present. Power dissipation in the faulty LED sink<br>increases and may hit TSD. Current in LED still regulated<br>to set level. FFn stays low as long as fault detected.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| С    | Short LED string                  | u 11                                                                                                                                                                    | No | Yes         | Low    | сс. 35<br>-      | . 33             | ۰۰ ۲۲<br>۱ | <i>и</i> "         | IC shutdown and<br>FFn pin goes<br>low. This state<br>remains latched<br>until VIN or any<br>ENx toggled. LED<br>pins rated for<br>45 V to protect IC<br>against this fault. | LEDx pin voltage on faulty string increases and IC detects<br>the fault. IC responds only by pulling FFn pin low as long<br>as fault present. Power dissipation in the faulty LED sink<br>increases and may hit TSD. Current in LED still regulated<br>to set level. FFn stays low as long as fault detected.<br>LED pins rated for 45 V to protect IC against this fault.                                                                                                                                                                                                                                                                                                                                                            |

| Grou | up 2 Faults Based o               | n LEDx Pin Voltage V <sub>LED(SC</sub>                                                                                                                                  | )  |             |        |                  |                  |            |                    |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| D    | Mid-LED-string<br>short-to-ground | V <sub>OUT</sub> > V <sub>OLED_dis</sub> and<br>any enabled LEDx pin<br>voltage < V <sub>LED(SC)</sub>                                                                  | No | Yes         | Low    | All Turn Off     | Operate Normally | Turn Off   | Operate Normally   | IC shutdown and<br>FFn pin goes<br>low. This state<br>remains latched<br>until VIN or any<br>ENx toggled.                                                                    | LEDx pin voltage on faulty string drops and IC detects the fault. For a brief time, $V_{OUT}$ increases due to open-loop operation. Q1 turns on harder as the LEDx pin voltage on faulty string drops below regulation. $V_{OUT}$ rises close to $V_{IN}$ . $V_{OUT}$ drops to regulation level after removing the faulty string from regulation loop. The faulty string removed from Q1 regulation loop and sinks turned off. During output overshoot time, Fault B may also be detected by the IC but it does not affect the operation. Faulty string will be out of Q1 loop regulation until voltage on faulty string rises above regulation level or VIN or any ENx toggled. FFn pin stays low as other string shorted to ground. |

| Е    | LEDx pin short-<br>to-ground      | <i>u</i> "                                                                                                                                                              | No | Yes         | Low    | ""               | ""               | ""         |                    | ss 33<br>-                                                                                                                                                                   | ц 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| F    | LED string open                   | ۰ ۲۲<br>۲                                                                                                                                                               | No | Yes         | Low    | ""               | ""               | ""         | ""                 | ss 33                                                                                                                                                                        | <u>с</u> и п                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| G    | LED common-<br>anode open         | u n                                                                                                                                                                     | No | Yes         | Low    | ۰۰ <sup>۲۲</sup> | ""               | sc 33      | " <sup>33</sup>    | u »                                                                                                                                                                          | Voltage on all LED pins drop below regulation level. $V_{OUT}$ rises close to $V_{IN}$ and stays at this level as all LEDx pins removed from regulation. Sinks remain active and internal gate of sink driver rails high. When a string connected back, $V_{OUT}$ controlled by this string. There will be a small LED current overshoot. FFn pin stays low if any string is open.                                                                                                                                                                                                                                                                                                                                                    |

#### Table 2: Fault Description (continued)

|   | FAULT                          | Detection Criterion                                                                | Auto-<br>Restart    | FFn<br>FAULT | LED<br>Sinks                                             | Ballast<br>MOSFET   | Operation                                                                                                                                                                                                                                                                                        |

|---|--------------------------------|------------------------------------------------------------------------------------|---------------------|--------------|----------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                | MODE State $\rightarrow$                                                           | 1 or 0              | 1 or 0       | 1 or 0                                                   | 1 or 0              | 1 or 0                                                                                                                                                                                                                                                                                           |

| н | String-to-<br>string short     | This condition is not detected                                                     | Operate<br>Normally | Normal       | Operate<br>Normally                                      | Operate<br>Normally | IC operates normally. LED currents in shorted string may not share same current                                                                                                                                                                                                                  |

|   | Thermal<br>Shutdown            | Junction<br>temperature<br>exceeds T <sub>JF</sub>                                 | Yes                 | Low          | All Turn<br>Off                                          | Turn Off            | IC shutdown and FFn pin goes low. This state remains<br>latched and re-enables when junction temperature drops<br>below 145°C. This is a non-latching fault, but this fault leads<br>to a Fault A condition if thermal shutdown is long enough to<br>allow the OUT capacitor to fully discharge. |

|   | Thermal<br>Derating            | Junction<br>temperature<br>exceeds T <sub>JM</sub>                                 | Operate<br>Normally | Normal       | LED<br>current<br>derated<br>based on<br>T <sub>J</sub>  | Operate<br>Normally | LED current derated based on junction temperature                                                                                                                                                                                                                                                |

|   | V <sub>IN</sub> Derating       | Input voltage V <sub>IN</sub><br>exceeds threshold<br>set by voltage on<br>VTH pin | Operate<br>Normally | Normal       | LED<br>current<br>derated<br>based on<br>V <sub>IN</sub> | Operate<br>Normally | LED current derated based on supply voltage and $V_{VTH}$ setting.                                                                                                                                                                                                                               |

|   | Undervoltage<br>Protection     | V <sub>BIAS</sub> below<br>V <sub>BIASSTART</sub>                                  | Yes                 | Low          | All Turn<br>Off                                          | Turn Off            | All faults cleared when this fault occurs. IC restarts when $V_{BIAS} > V_{BIASSTART}$                                                                                                                                                                                                           |

|   | V <sub>IN</sub><br>Overvoltage | Input voltage V <sub>IN</sub><br>exceeds V <sub>INOVth</sub><br>level              | Yes                 | Low          | All Turn<br>Off                                          | Turn Off            | This is a non-latching fault but this fault leads to a Fault A condition if the overvoltage is long enough to allow the OUT capacitor to fully discharge.                                                                                                                                        |

Notes:

If the non-latching fault condition causes OUT voltage to drop below V<sub>OUT(SC)</sub>, the IC will latch as described in Fault A.

Once faulty condition is detected, FFn goes low after fault blanking time. Fault blanking time for Fault A is 1 µs; fault blanking time for Fault B and C is 3 µs; fault blanking time for Fault D, E, F, and G is 65 µs.

• For non-latching part, ignore FFn status when duty cycle is below 5%.

• For non-latching part, it is recommended to use a small capacitor of 4.7 nF from FFn to GND with a 10 kΩ FFn pull-up resistor during dimming mode.

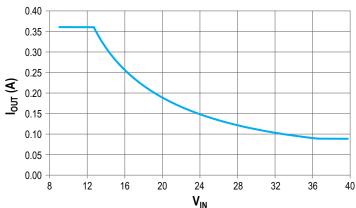

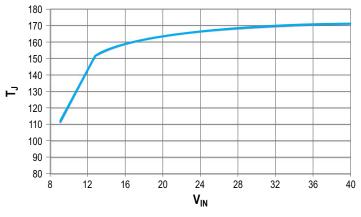

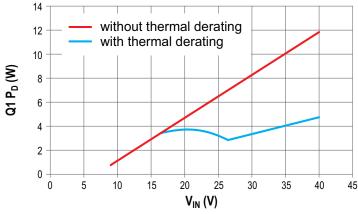

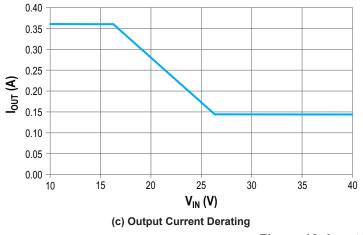

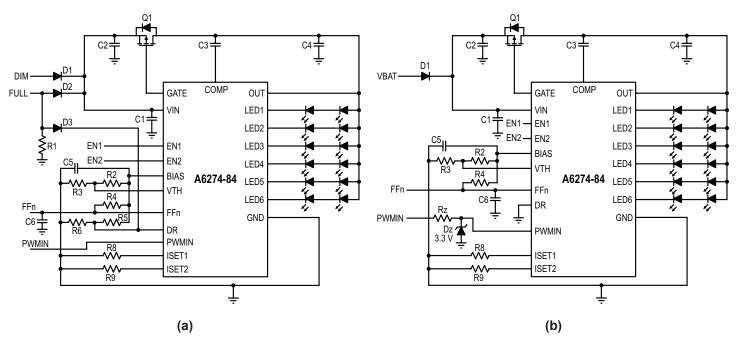

### Power Derating Based on $\rm T_{\rm J}$

An external MOSFET dissipates excess voltage ( $V_{IN}$ ,  $V_{LED}$ ,  $V_{LEDreg}$ ) and minimizes power loss in sinks. When an external MOSFET is not used, as shown in Figure 17, internal sinks drop

this excess voltage, and power dissipation in sinks increases. The A6274/84 derates the LED current based on junction temperature to extend its operating range. A typical example (below) shows LED current derating and junction temperature of the IC ( $T_J$ ) at different VIN conditions.

### **EXAMPLE 1**

| Table 3: LED Current Derating and Junction | Temperature of the IC (T | J) at Different V <sub>IN</sub> Conditions |

|--------------------------------------------|--------------------------|--------------------------------------------|

|--------------------------------------------|--------------------------|--------------------------------------------|

| Value | Units                             | Description                                                                                                                           |

|-------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 7     | V                                 | Total LED string voltage at desired LED current                                                                                       |

| 0.36  | А                                 | Total LED current                                                                                                                     |

| 90    | °C                                | Ambient temperature                                                                                                                   |

| 30    | °C/W                              | Junction-to-ambient thermal resistance for the IC                                                                                     |

| 154   | °C                                | Junction temperature at which LED current drops to 90% level. Refer to Figure 8.                                                      |

| 9     | V                                 | Minimum input voltage                                                                                                                 |

| 40    | V                                 | Maximum input voltage                                                                                                                 |

|       | 7<br>0.36<br>90<br>30<br>154<br>9 | 7         V           0.36         A           90         °C           30         °C/W           154         °C           9         V |

## (a) Output combined LED current derating with supply voltage variation. LED current drop at higher $V_{\rm IN}$ due to excessive power dissipation.

(c) Output combined LED current derating with junction temperature of the IC

#### Figure 11: Thermal Derating

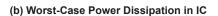

# Power Derating Based on Input Supply Voltage $\rm V_{\rm IN}$

The A6274/84 derates LED current based on the supply voltage and reference voltage on the VTH pin. Power dissipation in the

external transistor can be limited at higher input voltage. The example below shows the selection of  $V_{\rm VTH}$  to limit MOSFET junction temperature below 140°C. Refer to Figure 1 for typical application.

### EXAMPLE 2

| Table 4: LED Current Derating | and Junction Temperatu | re of the IC (T <sub>J</sub> ) at Differe | nt V <sub>IN</sub> Conditions |

|-------------------------------|------------------------|-------------------------------------------|-------------------------------|

|-------------------------------|------------------------|-------------------------------------------|-------------------------------|

| Symbol               | Value | Units | Description                                                              |

|----------------------|-------|-------|--------------------------------------------------------------------------|

| $V_{LED}$            | 7     | V     | Total LED string voltage at desired LED current                          |

| I <sub>OUT</sub>     | 0.36  | A     | Total LED current                                                        |

| T <sub>A</sub>       | 90    | °C    | Ambient temperature                                                      |

| R <sub>θJA</sub>     | 10    | °C/W  | Junction-to-ambient thermal resistance for MOSFET                        |

| V <sub>LEDreg</sub>  | 0.4   | V     | LEDx pin regulation voltage                                              |

| V <sub>IN(MIN)</sub> | 9     | V     | Minimum input voltage                                                    |

| V <sub>IN(MAX)</sub> | 40    | V     | Maximum input voltage                                                    |

| V <sub>VTH</sub>     | 1.64  | V     | External voltage applied to VTH pin                                      |

| V <sub>INth(L)</sub> | 18    | V     | Input voltage at which LED current drops to 90% level; refer to Figure 7 |

0.35

0.30

0.25

0.20

0.10

0.05

0.00 + 10

15

Worst-Case P<sub>D</sub> in IC (W)

25

V<sub>IN</sub> (V)

30

35

40

20

#### Figure 12: Input Voltage Derating

### Linear Current Regulator and Controller for Automotive LED Arrays

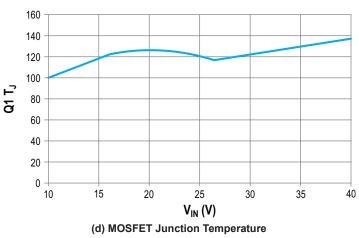

### **APPLICATION CIRCUITS**

#### **External PWM**

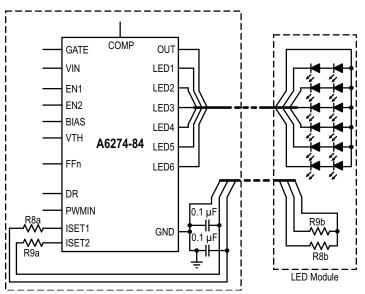

The PWMIN pin senses logic level input and switches to external PWM mode. PWM frequency and duty cycle are set by logic input on the PWMIN pin when the DR pin voltage is less than 3.6 V.

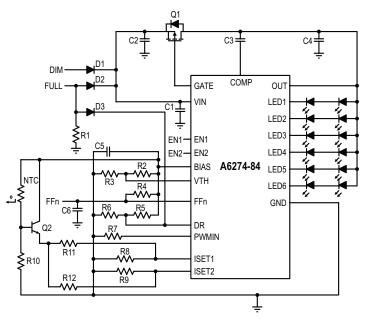

Figure 13a shows an application circuit to control dimming with an external logic level PWM signal in DIM mode and FULL mode controlled through DR pin. Duty cycle and frequency applied on PWMIN pin controls LED current during DIM mode. In FULL mode, LEDs always operate with 100% duty cycle.

Figure 13b shows an application circuit where external PWM controls LED dimming in FULL and DIM modes. Use Rz = 0 and open Dz for PWM signal level below 5 V. Rz-Dz should be used to limit PWMIN pin voltage when battery-referred PWM signal is applied.

Figure 13: Dimming with External PWM

### Linear Current Regulator and Controller for Automotive LED Arrays

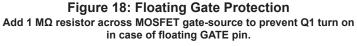

# Using One Reference Resistor for Setting Current in LED1-6

The A6274 and A6284 have two LED groups: LED1-3 and LED4-6. The peak LED current can be set separately using ISET1 and ISET2 respectively. If the same LED current is required for both groups, as shown in Figure 14, connect ISET2 to BIAS. This disables the ISET2 reference from the pin and internally uses the same reference as ISET1. Using a single resistor in setting current through all LEDs improves matching between the two LED groups.

# MOSFET Protection by External Thermal Derating

The A6274/84 has a built-in thermal-derating function which works on the junction temperature of the IC. If the MOSFET is placed away from the IC, the junction temperature of the MOS-FET and IC will be different, and thermal derating may not work effectively to protect the MOSFET.

An external circuit shown below can be placed close to the MOSFET to sense temperature and foldback LED current to limit power dissipation.

An NTC is placed close to Q1. The gain of the NTC and resistor ratios R11 to R8 set the derating slope. The NTC determines the thermal derating threshold. A typical application circuit for the thermal derating for the MOSFET is shown in Figure 15.

As temperature increases, NTC resistance drops. When voltage on Q2 base increases above  $\sim 1.6$  V, Q2 turns on. Current through R11 is given by:

$$(VB - 0.4 - 1.2) \div R11$$

where VB is the voltage on the base of transistor Q2. This current reduces current sourced by the ISETx pins, and LED current drops proportionately.

Current through ISET1 pin is given by:

$$ISET1 = 1.2 \div R8 - (VB - 0.4 - 1.2) \div R11$$

.

Similarly, current through ISET2 pin is given by:

$$ISET2 = 1.2 \div R9 - (VB - 0.4 - 1.2) \div R12$$

Figure 14: Using Common ISET Reference

Figure 15: External Power Derating

### Linear Current Regulator and Controller for Automotive LED Arrays

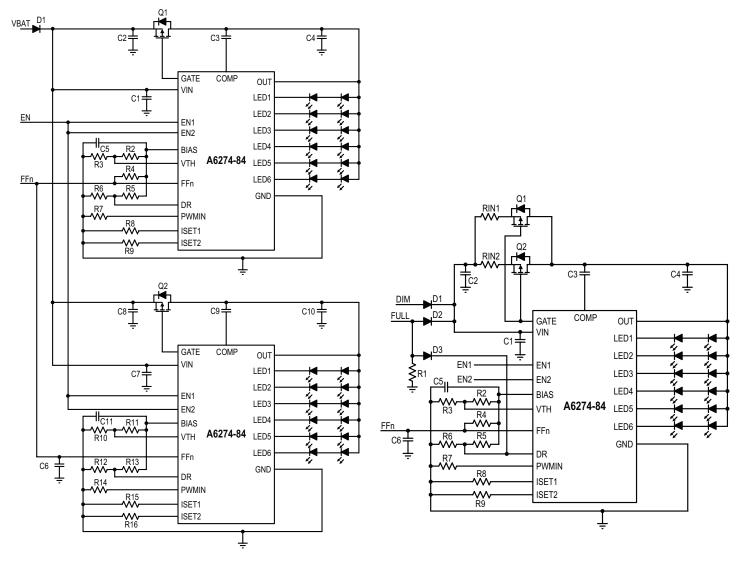

# Connecting Multiple ICs and External PMOS in Parallel Configuration

For larger lighting assemblies or to drive higher current, multiple ICs can be paralleled by connecting open-drain FFn pins of all

the ICs together as shown in Figure 16a. Up to 20 ICs can be used in parallel configuration.

For better thermal performance of external PMOS, two PMOS can be paralleled as shown in Figure 16b.

Figure 16a: Parallel Connection for Multiple IC Operation Figure 16b: Two External PMOS in Parallel Configuration

### **Operation without External P-Channel MOSFET**

An external P-channel MOSFET should be used to minimize power dissipation in the IC; however, the A6274/84 can be used without an external MOSFET for low-power applications, as shown in Figure 17. The IC will detect but not be able to protect external components in case of A, D, and E faults. See Fault Table for more details.

Connect the GATE and COMP pins to VIN when an external PMOS is not connected. When the PMOS preregulator is not

Figure 17: Operation without External P-Channel MOSFET Connect COMP and GATE pins to VIN when external PMOS not used.

used, the LED string short faults B and C will be disabled.

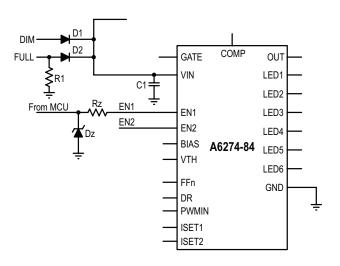

#### **Binning Resistor Arrangement**

An external binning resistor can be connected in series with the ISETx pins as shown in Figure 19, to set appropriate current through various LED batches.

Figure 19: Application Circuit for Binning Current-setting resistor can be placed on LED board for different bins of LEDs.

#### Figure 20: Application Circuit to Protect Microcontroller in Case of Accidental VIN Short to EN1

EN1 and VIN pins are close to each other. EN1 pin is rated for full supply voltage but external driving microcontroller may be damaged with VIN short. Adding a zener clamp will protect MCU.

#### Figure 21 : Application circuit to prevent false latching state when $V_{OUT} < V_{OUT(SC)}$ .

If any operating or fault condition causes OUT voltage to drop below V<sub>OUT(SC)</sub>, the IC will detect this as a MOSFET drain short-to-ground fault. The IC will latch off as described in Fault-A in table 2. Adding a 1 MΩ bypass resistor across external MOSFET will keep V<sub>OUT</sub> > V<sub>OUT(SC)</sub> level and prevent false latching. Adding this resistor will not affect normal MOSFET drain short-to-ground (Fault-A) detection.

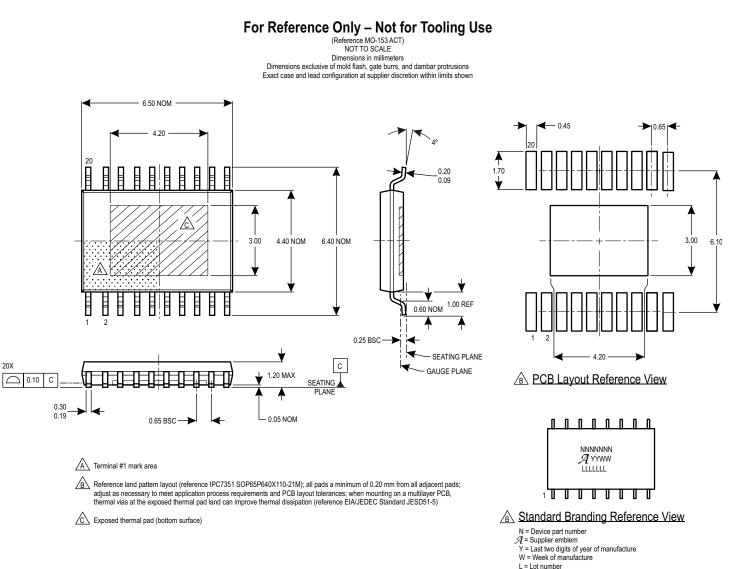

#### PACKAGE OUTLINE DRAWING

Figure 22: Package LP, 20-Pin eTSSOP with Exposed Thermal Pad

#### **Revision Table**

| Number | Date              | Description                                                           |  |

|--------|-------------------|-----------------------------------------------------------------------|--|

| -      | July 8, 2016      | Initial release                                                       |  |

| 1      | September 9, 2016 | 6 Added footnote to PWM Duty Cycle D <sub>PWM5</sub> symbol (page 6). |  |

Copyright ©2016, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

#### www.allegromicro.com