# AM25LS2568, AM25LS2569

## Four-Bit Up/Down Counters with Three-State Outputs

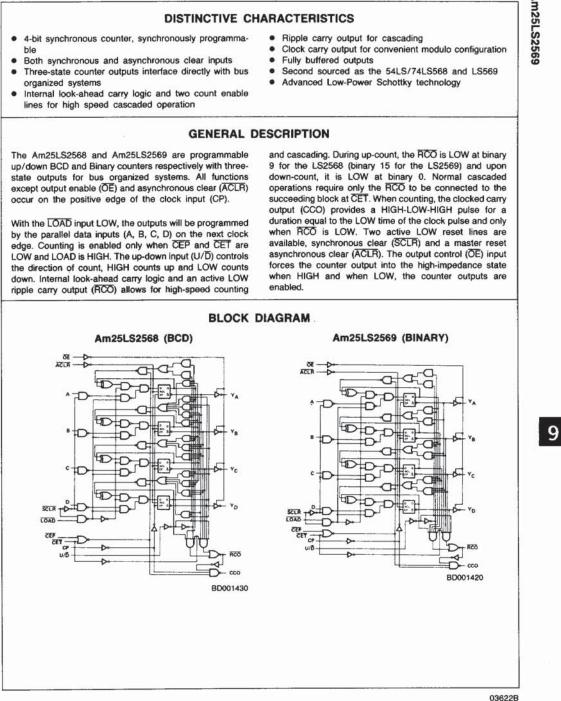

The AM25LS2568 and AM25LS2569 are programmable up/down BCD and Binary counters respectively with three-state outputs for bus organized systems. All functions except output enable  $(\overline{OE})$  and asynchronous clear ( $\overline{ACLR}$ ) occur on the positive edge of the clock input (CP).

With the  $\overline{\text{LOAD}}$  input LOW, the outputs will be programmed by the parallel data inputs (A, B, C, D) on the next clock edge. Counting is enabled only when  $\overline{\text{CEP}}$  and  $\overline{\text{CET}}$  are LOW and LOAD is HIGH. The up-down input (U/D) controls the direction of count, HIGH counts up and LOW counts down.

### Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

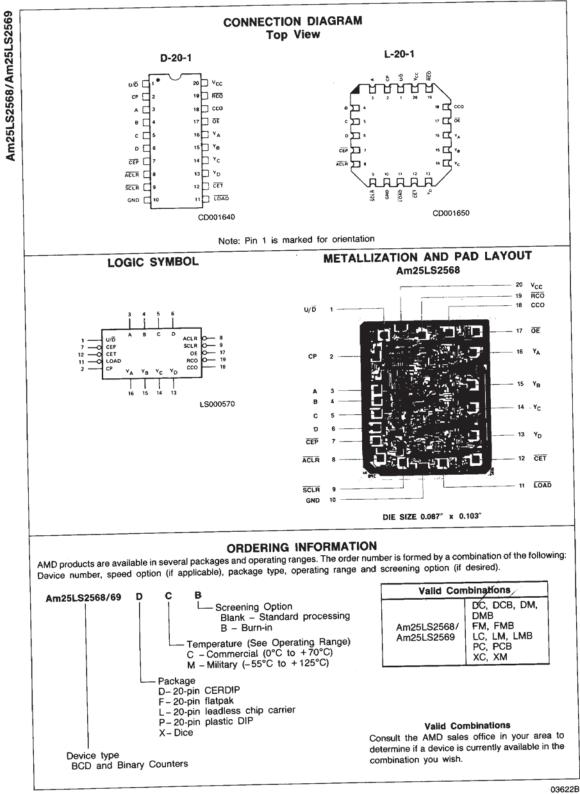

# Am25LS2568/Am25LS2569

Four-Bit Up/Down Counters with Three-State Outputs

9-157

Refer to Page 13-1 for Essential Information on Military Devices

9-158

Refer to Page 13-1 for Essential Information on Military Devices

|                  |                                                                      |     | PIN DESCRIPTION                                                                                                               |

|------------------|----------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| Pin No.          | Name                                                                 | 1/0 | Description                                                                                                                   |

| 3, 4, 5, 6       | A, B, C, D                                                           | 1   | The four programmable data inputs.                                                                                            |

| 7                | CEP                                                                  | ł   | Count Enable Parallel. Can be used to enable and inhibit counting in high speed cascaded operation. CEP must be LOW to count. |

| 12               | CET                                                                  | I   | Count Enable Trickle. Enables the ripple carry output for cascaded operation. Must be LOW to count.                           |

| 2                | CP                                                                   | 1   | Clock Pulse. All synchronous functions occur on the LOW-to-HIGH transition of the clock.                                      |

| 11               | LOAD                                                                 | 1   | Enables parallel load of counter outputs from data inputs on the next clock edge. Must be HIGH to count.                      |

| 1                | U/D                                                                  | I   | Up/Down Count Control. HIGH counts up and LOW counts down.                                                                    |

| 8                | ACLR                                                                 | Ι   | Asynchronous Clear. Master reset of counters to zero when ACLR is LOW, independent of the clock.                              |

| 9                | SCLR                                                                 | I   | Synchronous clear of counters to zero on the next clock edge when SCLR is LOW.                                                |

| 17               | ŌE                                                                   | i   | A HIGH on the output control sets the four counter outputs in the high-impedance, and a LOW enables the output.               |

| 16, 15<br>14, 13 | Y <sub>A</sub> , Y <sub>B</sub> ,<br>Y <sub>C</sub> , Y <sub>D</sub> | 0   | The four counter outputs.                                                                                                     |

| 19               | RCO                                                                  | 0   | Ripple Carry Output. Output will be LOW on the maximum count on up-count. Upon down-count, RCO is LOW at 0000.                |

| 18               | cco                                                                  | 0   | Clock Carry Output. While counting and RCO is LOW, CCO will follow the clock HIGH-LOW-HIGH transition.                        |

### Am25LS2568/2569 FUNCTION TABLE

| Clear         X           (ASYNC)         X           Clear         X           Clear         X           Load         0           Load         0           Count Up         1           Inhibit         1           Inhibit         1           Output         1           Disable         X           X = Don't Care         Dn = Do thru D3           Notes:         1.           Regis         2.           Follow         3.           1001         2. | X         X           X         X           X         X           X         X           0         X           0         X           0         X           0         X           0         X           0         X           0         X           0         X           1         0           1         0           1         1           1         1           X         X           V-to-HIGH tra           3         input level p           ister performs           cucck         1           V for one full             | X         X           X         X           1         3           0         1           0         1           0         1           0         1           1         3           0         1           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3 | 1         0           0         1           1         1           0         1           1         1           1         1           1         1           1         1           X         1           X         1           X         1           X         1           X         1           X         X           clock         transition       | CLEAR           X           0           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1 <th>OE, but OI</th> <th><b>D</b><sub>0</sub><br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X</th> <th>Next i<br/>No cha</th> <th>ower (</th> <th>D<sub>3</sub><br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X<br/>X</th> <th>CP<br/>X<br/>X<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1<br/>1</th> <th>Q0<br/>0<br/>0<br/>0<br/>1<br/>Z</th> <th>Q1<br/>0<br/>0<br/>0<br/>0<br/>0<br/>1<br/>Q<sub>n</sub> =<br/>0<br/>1<br/>Q<sub>n</sub> =<br/>0<br/>1<br/>Q<sub>n</sub> =<br/>0<br/>1<br/>N.<br/>N.<br/>N.<br/>N.<br/>Z<br/>=<br/>equence</th> <th>0<br/>1<br/>+ 1<br/>- 1<br/>C.<br/>C.<br/>C.<br/>C.<br/>Z</th> <th>Q3<br/>0<br/>0<br/>0<br/>1(3)<br/>Z</th> <th>RC<br/>1<br/>0<br/>1<br/>0<br/>1<br/>0<br/>0<br/>(4)<br/>(6)<br/>N.C.<br/>N.C.<br/>N.C.<br/>N.C.</th> <th>CLOCK<br/>CARRY<br/>1<br/>1 (2)<br/>1 (2)<br/>1 (2)<br/>(5)<br/>(5)<br/>(5)<br/>1<br/>1<br/>1<br/>1<br/>1<br/>N.C.</th> | OE, but OI                                                                                       | <b>D</b> <sub>0</sub><br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X           | Next i<br>No cha                                                                                 | ower (                                                                  | D <sub>3</sub><br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X      | CP<br>X<br>X<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | Q0<br>0<br>0<br>0<br>1<br>Z | Q1<br>0<br>0<br>0<br>0<br>0<br>1<br>Q <sub>n</sub> =<br>0<br>1<br>Q <sub>n</sub> =<br>0<br>1<br>Q <sub>n</sub> =<br>0<br>1<br>N.<br>N.<br>N.<br>N.<br>Z<br>=<br>equence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0<br>1<br>+ 1<br>- 1<br>C.<br>C.<br>C.<br>C.<br>Z                         | Q3<br>0<br>0<br>0<br>1(3)<br>Z | RC<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>(4)<br>(6)<br>N.C.<br>N.C.<br>N.C.<br>N.C. | CLOCK<br>CARRY<br>1<br>1 (2)<br>1 (2)<br>1 (2)<br>(5)<br>(5)<br>(5)<br>1<br>1<br>1<br>1<br>1<br>N.C. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| (ASYNC)         X           Clear         X           (SYNC)         X           Load         0           Load         0           Count Up         1           Inhibit         1           Inhibit         1           Output         1           Disable         X           T = CLOCK LOW-           X = Don't Care           Dn = D0 thru D3           Notes:         1. Regis           1001         4. LOW           5. Follow                        | X         X           X         X           X         X           0         X           0         X           0         X           0         X           0         X           0         X           0         X           0         X           0         X           1         0           1         0           1         1           1         1           X         X           V-to-HIGH tra           3 input level p           ister performs           cWork CLOCK i           1         1           V for one full | X         X           X         X           1         3           0         0           0         0           0         1           0         1           1         3           0         1           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           1         3           2         ansition           prior to c         s all corr           if CET = 1         1                                                                                                                                               | D         O           1         1           0         1           1         1           1         1           1         1           X         1           X         1           X         1           X         1           X         1           X         1           X         X           clock         transition           rect logic for or | X           0           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1           1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                  | X<br>X<br>X<br>0<br>1<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>0<br>1<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>0<br>1<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | x<br>x<br>x<br>0<br>1(3)<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x | X<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1  | 0<br>0<br>0<br>1<br>Z       | 0<br>0<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0<br>0<br>0<br>1<br>+ 1<br>- 1<br>C.<br>C.<br>C.<br>C.<br>Z               | 0<br>0<br>1(3)                 | 0<br>1<br>0<br>(4)<br>(6)<br>N.C.<br>N.C.<br>N.C.<br>N.C.                           | 1<br>(2)<br>1<br>(2)<br>(2)<br>(5)<br>(5)<br>1<br>1<br>1<br>1<br>1                                   |

| (SYNC)         X           Load         0           Load         0           Count Up         1           Count Down         1           Inhibit         1           Output         1           Disable         X           D = Do thru D3         Notes: 1. Regis           Notes: 1. Regis         2. Follow           3. 1001         4. LOW           5. Follow         5. Follow                                                                       | X         X           0         X           0         X           1         0           1         0           1         0           1         1           1         1           1         1           1         1           1         1           X         X           W-to-HIGH transport           a input level performs           ows CLOCK in the LS68.           V for one full                                                                                                                                        | X         1           1         2           0         1           0         2           1         2           0         1           0         2           1         2           x         3           ansition         prior to c           s all correction         s all correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0         1           X         1           0         1           1         1           1         1           X         1           X         1           X         1           X         1           X         1           X         X           clock transition           rect logic for of                                                     | 0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0      | X<br>X<br>0<br>1<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                | X<br>X<br>0<br>1<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                | X<br>0<br>1<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                     | X<br>0<br>1(3)<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                     | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                 | 0<br>0<br>1<br>Z            | 0<br>Q <sub>n</sub> =<br>0<br>1<br>Q <sub>n</sub><br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>= D <sub>n</sub><br>0<br>1<br>+ 1<br>-1<br>C.<br>C.<br>C.<br>C.<br>Z | 0 1(3)                         | 0<br>1<br>0<br>(4)<br>(6)<br>N.C.<br>N.C.<br>N.C.<br>N.C.                           | 1<br>(2)<br>(2)<br>(2)<br>(5)<br>(5)<br>1<br>1<br>1<br>1                                             |

| Load         0           Load         0           0         0           Count Up         1           Count Down         1           Inhibit         1           Inhibit         1           Output         X           Disable         X           T = CLOCK LOW-           X = Don't Care           Dn = D0 thru D3           Notes:         1. Regis           2. Follow           3. 1001           4. LOW           5. Follow                           | 0 X<br>0 X<br>1 0<br>1 0<br>1 1<br>1 1<br>1 1<br>X X<br>V-to-HIGH tra<br>3 input level p<br>ister performs<br>ows CLOCK i<br>1 for LS68.                                                                                                                                                                                                                                                                                                                                                                                      | 0<br>0<br>0<br>0<br>1<br>2<br>x<br>2<br>x<br>2<br>ansition<br>prior to c<br>s all correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 1<br>1 1<br>1 1<br>1 1<br>0 1<br>X 1<br>X 1<br>X 1<br>X X<br>clock transition<br>rect logic for of                                                                                                                                                                                                                                               | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>N-1 =                                | 0<br>1<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>Next i<br>Next i                               | 0<br>1<br>X<br>X<br>X<br>X<br>X<br>X<br>X                               | 0<br>1(3)<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>x                               | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>X                                                              | 1<br>Z                      | 0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0<br>1<br>+ 1<br>- 1<br>C.<br>C.<br>C.<br>C.<br>Z                         | 1(3)                           | 0<br>(4)<br>(6)<br>N.C.<br>N.C.<br>N.C.                                             | 1<br>(2)<br>(2)<br>(5)<br>1<br>1<br>1                                                                |

| Count Down         1           Inhibit         1           Inhibit         1           Output         X           Disable         X           T = CLOCK LOW-X = Don't Care         Don thru D3           Notes:         1. Regis           2. Follow         3. 1001           4. LOW         5. Follow                                                                                                                                                     | 1         0           1         0           1         1           1         1           X         X           W-to-HIGH tra           a input level g           ister performs           ows CLOCK i           1 for LS68.           V for one full                                                                                                                                                                                                                                                                           | 0     0       1     2       0     1       1     2       x     2       ansition       prior to c       s all correction       if CET = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 1<br>X 1<br>X 1<br>X 1<br>X X<br>clock transition<br>rect logic for a                                                                                                                                                                                                                                                                            | 1<br>1<br>1<br>1<br>X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                  | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X      | X<br>X<br>X<br>X<br>= Next<br>Next i                                                             | X<br>X<br>X<br>X<br>higher                                              | X<br>X<br>X<br>X<br>X                                                                | 1<br>1<br>1<br>X                                                                                  | nary s                      | Qn<br>N.<br>N.<br>Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - 1<br>C.<br>C.<br>C.<br>C.<br>Z                                          | Z                              | (6)<br>N.C.<br>N.C.<br>N.C.                                                         | (5)<br>1<br>1<br>1                                                                                   |

| Inhibit         1           Inhibit         1           Output         1           Disable         X           Disable         X           T = CLOCK LOW-         X = Don't Care           Dn = Do thru D3         Notes: 1. Regis           Notes: 1. Regis         2. Follow           3. 1001         4. LOW           5. Follow         5. Follow                                                                                                       | 1     0       1     1       1     1       1     1       X     X   W-to-HIGH tra   ister performs   ows CLOCK i    1 for LS68.   V for one full                                                                                                                                                                                                                                                                                                                                                                                | 1 2<br>0 2<br>1 2<br>x 2<br>ansition<br>prior to c<br>s all corre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | X 1<br>X 1<br>X 1<br>X X<br>Clock transition                                                                                                                                                                                                                                                                                                       | 1<br>1<br>1<br>X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0<br>0<br>1<br>OE, but O                                                                         | X<br>X<br>X<br>X<br>N + 1 =                                                                      | X<br>X<br>X<br>= Next<br>Next i                                                                  | X<br>X<br>X<br>higher                                                   | X<br>X<br>X<br>X                                                                     | 1<br>1<br>X                                                                                       | nary s                      | N.<br>N.<br>Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | C.<br>C.<br>C.<br>Z                                                       | Z                              | N.C.<br>N.C.<br>N.C.                                                                | 1<br>1<br>1                                                                                          |

| Inhibit         1           Output         1           Disable         X           Disable         X           T = CLOCK LOW-<br>X = Don't Care<br>Dn = Do thru D3           Notes:         1. Regis           2. Follow           3. 1001           4. LOW           5. Follow                                                                                                                                                                             | 1 1<br>1 1<br>X X<br>W-to-HIGH tra<br>3 input level p<br>ister performs<br>ows CLOCK i<br>1 for LS68.<br>V for one full                                                                                                                                                                                                                                                                                                                                                                                                       | 0 2<br>1 2<br>ansition<br>prior to c<br>s all correct<br>if CET = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | X 1<br>X 1<br>X X<br>clock transition                                                                                                                                                                                                                                                                                                              | 1<br>1<br>X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                  | X<br>X<br>X<br>n+1=<br>I.C. = N                                                                  | X<br>X<br>= Next<br>Next i<br>No cha                                                             | X<br>X<br>higher                                                        | X<br>X<br>X                                                                          | t<br>tin bi                                                                                       | nary s                      | N.<br>N.<br>Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | C.<br>C.<br>Z                                                             | Z                              | N.C.<br>N.C.                                                                        | 1                                                                                                    |

| Disable ↑<br>t = CLOCK LOW-<br>X = Don't Care<br>D <sub>n</sub> = D <sub>0</sub> thru D <sub>3</sub><br>Notes: 1. Regis<br>2. Follow<br>3. 1001<br>4. LOW<br>5. Follow                                                                                                                                                                                                                                                                                      | V-to-HIGH tra<br>input level p<br>ister performs<br>ows CLOCK i<br>1 for LS68.<br>V for one full                                                                                                                                                                                                                                                                                                                                                                                                                              | ansition<br>prior to c<br>s all corre<br>if CET = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | clock transition                                                                                                                                                                                                                                                                                                                                   | n<br>any state of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                  | n + 1 =<br>n_1 =<br>I.C. = N                                                                     | Next<br>Next i                                                                                   | higher<br>ower                                                          | r coun                                                                               | t in bi                                                                                           | nary s                      | equend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | :0                                                                        | Z                              | N.C.                                                                                | N.C.                                                                                                 |

| $\label{eq:constraint} \begin{array}{l} \uparrow = \text{CLOCK LOW-} \\ \textbf{X} = \text{Don't Care} \\ \textbf{D}_n = \textbf{D}_0 \ \text{thru} \ \textbf{D}_3 \\ \textbf{Notes: 1. Regis} \\ 2. \ \text{Follow} \\ 3. \ 1001 \\ 4. \ \text{LOW} \\ \textbf{5. \ Follow} \end{array}$                                                                                                                                                                   | 3 input level p<br>ister performs<br>ows CLOCK i<br>1 for LS68.<br>V for one full                                                                                                                                                                                                                                                                                                                                                                                                                                             | prior to c<br>s all corre<br>if CET = t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | rect logic for a                                                                                                                                                                                                                                                                                                                                   | any state of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | OE, but OI                                                                                       | n_1 =<br>I.C. = N                                                                                | Next i<br>No cha                                                                                 | ower (                                                                  | r coun<br>count                                                                      | t in bi<br>in bina                                                                                | nary sec                    | equence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                                         | _                              |                                                                                     |                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                  | , –                                                                                              |                                                                                                  |                                                                         |                                                                                      |                                                                                                   |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |                                |                                                                                     |                                                                                                      |

# Am25LS2568/Am25LS2569

03622B Refer to Page 13-1 for Essential Information on Military Devices

### ABSOLUTE MAXIMUM RATINGS

# Continuous .....-0.5V to +7.0V

DC Voltage Applied to Outputs For High Output State .....-0.5V to +V<sub>CC</sub> max

DC Input Current .....-30mA to +5.0mA

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device

#### **OPERATING RANGES**

### Commercial (C) Devices

Temperature .....0°C to +70°C Supply Voltage ...... + 4.75V to + 5.25V

Military (M) Devices Temperature .....-55°C to +125°C

ality of the device is guaranteed.

### DC CHARACTERISTICS over operating range unless otherwise specified

| arameters     | Description                                                                                                                                                         | Test                                                            | Cond                  | tions (No           | te 2) |             | Min          | Typ<br>(Note 1) | Max         | Units |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------|---------------------|-------|-------------|--------------|-----------------|-------------|-------|

| al allietel 8 |                                                                                                                                                                     |                                                                 | T                     | MIL, IOH =          |       |             | 2.4          | 3.4             |             |       |

|               |                                                                                                                                                                     | V <sub>CC</sub> = MIN                                           | Yi                    | COM'L, IOH = -2.6mA |       |             | 2.4          | 3.2             |             | Matte |

| VOH           | Output HIGH Voltage                                                                                                                                                 | VIN - VIH<br>of VIL                                             | RCO.                  |                     |       | MIL         | 2.5          | 3.4             |             | Volts |

|               |                                                                                                                                                                     |                                                                 | 000                   | IOH = -44           | OμA   | COM'L       | 2.7          | 3.4             |             |       |

|               |                                                                                                                                                                     |                                                                 |                       | IOL = 4.0m          | hΑ    |             |              |                 | 0.4         | Valla |

| VOL           | Output LOW Voltage                                                                                                                                                  | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IH</sub> or V | IOL = 8.0m            | -                   |       |             |              | 0.45            | Volts       |       |

| VIH           | Input HIGH Level                                                                                                                                                    | Guaranteed in<br>voltage for all                                | cal HIGH              | 02                  |       |             |              |                 | Volts       |       |

|               |                                                                                                                                                                     | Guaranteed in                                                   | MIL MIL               |                     |       |             |              | 0.7             | Volts       |       |

| VIL           | Input LOW Level                                                                                                                                                     | voltage for all                                                 |                       |                     | CO    | M'L         |              |                 | 0.8         |       |

| VI            | Input Clamp Voltage                                                                                                                                                 | Vcc = MIN, I                                                    | N = -18               | mA                  |       |             |              |                 | - 1.5       | Volts |

| ¥1            |                                                                                                                                                                     | 1                                                               |                       | ACLR, OF            |       |             |              |                 | -0.3        |       |

| 3             | Land LOW Current                                                                                                                                                    | V <sub>CC</sub> = MAX,                                          |                       | A, B, C,            | D, CF | , CEP       |              |                 | -0.4        | mA    |

| հե            | Input LOW Current                                                                                                                                                   | VIN = 0.4V                                                      |                       | CET, SCI            |       |             |              |                 | -0.65       |       |

| lui .         | Input HIGH Current                                                                                                                                                  | VCC = MAX.                                                      | VIN = 2.3             | V                   |       |             |              |                 | 20          | μA    |

| <u>чн</u>     | Input HIGH Current                                                                                                                                                  | VCC = MAX, V                                                    |                       |                     | 1.000 |             | 11           |                 | 0.1         | mA    |

| կ             |                                                                                                                                                                     | 1.00                                                            |                       | Vo = 0.4            | 1     |             |              |                 | - 20        |       |

| loz           | Off-State (High-Impedance)<br>Output Current                                                                                                                        | V <sub>CC</sub> = MAX                                           | V <sub>0</sub> = 2.4V |                     |       |             |              | 20              | μΑ          |       |