|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          | REVIS                               | SIONS              | ;                                |                       |                       |              |                |                    |        |  |

|----------------------------|--------------|---------|-------------|------------------|----------------------------------------------|---------------------|---------------------------|-----------------|------|-------|--------------------------|-------------------------------------|--------------------|----------------------------------|-----------------------|-----------------------|--------------|----------------|--------------------|--------|--|

|                            |              |         |             | L                | .TR                                          |                     |                           |                 | DESC | RIPTI | ON                       |                                     |                    |                                  | D                     | ATE                   |              |                | APPR               | OVED   |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

| Prepared                   | l in acco    | rdanc   | o with      | V CIVIE A        | 14 24                                        |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       |              |                |                    |        |  |

| Перагеи                    | i iii accc   | Tuaric  | C WILLI     | AOIVIL I         | 14.24                                        |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       | Ve           | andor i        | tem dr             | awina  |  |

| REV                        |              | —       |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       | Ve           | endor i        | tem dr             | awing  |  |

| PAGE                       | +            |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       | Ve           | endor i        | tem dr             | rawing |  |

| REV                        |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       | Ve           | endor i        | tem dr             | rawing |  |

|                            |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       | Ve           | endor i        | item dr            | rawing |  |

| PAGE                       |              |         |             |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       | Ve           | endor i        | tem dr             | rawing |  |

|                            | ATUS         |         | REV         |                  |                                              |                     |                           |                 |      |       |                          |                                     |                    |                                  |                       |                       | Ve           | endor i        | tem dr             | rawing |  |

| PAGE<br>REV STA<br>OF PAGE |              | _       | REV         |                  | 1                                            | 2                   | 3                         | 4               | 5    | 6     | 7                        | 8                                   | 9                  | 10                               |                       |                       | Ve           | endor i        | tem dr             | rawing |  |

| REV STA                    | ES           | _       | PAGE        | PREPAR           | ED BY                                        | ,                   |                           |                 | 5    | 6     | 7                        | 8                                   |                    | 10<br><b>LA L</b>                | AND                   | AND                   |              |                |                    | rawing |  |

| REV STA                    | ES           | _       | PAGE        |                  | ED BY                                        | ,                   | 3<br>Nguye                |                 | 5    | 6     | 7                        | 8                                   | D                  | LA L                             |                       |                       | ) MA         | RITIN          |                    |        |  |

| PMIC N/A                   | A date of c  | drawing | PAGE        |                  | ED BY                                        | Phu H.              | Nguy                      | en              | 5    | 6     | 7<br><b>TIT</b>          |                                     | D                  | LA L                             |                       |                       | ) MA         | RITIN          | ME                 |        |  |

| PMIC N/A                   | A  date of c | drawing | PAGE<br>F   | PREPAR           | RED BY                                       | Phu H.<br>Phu H.    |                           | en              | 5    | 6     | TIT                      | LE<br>CROC                          | DI<br>COL          | LA LA<br>LUME                    | BUS,<br>DIGIT         | OHIO                  | ) MA<br>O 43 | RITIN<br>3218- | ME<br>3990<br>DETE | СТОІ   |  |

| PMIC N/A                   | A date of c  | drawing | PAGE<br>F   | PREPAR           | RED BY F F F F F F F F F F F F F F F F F F F | Phu H.<br>Phu H.    | Nguy                      | en<br>en        | 5    | 6     | TIT<br>MIC<br>FRE        | LE<br>CROC                          | DI<br>COL<br>CIRCI | LA LA<br>LUME                    | BUS,<br>DIGIT         | OHIO                  | ) MA<br>O 43 | RITIN<br>3218- | ME<br>3990         | СТОІ   |  |

| PMIC N/A                   | A  date of c | drawing | PAGE<br>F   | PREPAR           | ED BY F /ED BY Th                            | Phu H. Phu H. homas | Nguyo<br>Nguyo<br>s M. Ho | en<br>en        | 5    | 6     | TIT<br>MIC<br>FRE<br>SIL | LE<br>ROC                           | DI<br>COL<br>CIRCI | LA LA<br>LUME                    | BUS,<br>DIGIT         | OHIO                  | ) MA<br>O 43 | RITIN<br>3218- | ME<br>3990<br>DETE | СТОІ   |  |

| PMIC N/A                   | A  date of c | drawing | PAGE<br>F   | PREPAR<br>CHECKE | ED BY F /ED BY Th                            | Phu H. Phu H. homas | Nguyo<br>Nguyo<br>s M. Ho | en<br>en        | 5    | 6     | TIT<br>MIC<br>FRE<br>SIL | LE<br>CROC<br>EQUE                  | DI<br>COL<br>CIRCI | LA LA<br>LUME<br>UIT, [<br>/ SYN | BUS,<br>DIGIT<br>NTHE | OHIO                  | PHAER,       | RITIN<br>3218- | ME<br>3990<br>DETE | СТОІ   |  |

| PMIC N/A                   | A  date of c | drawing | PAGE<br>g ( | CHECKE<br>APPROV | ED BY F /ED BY Th                            | Phu H. Phu H. homas | Nguyo<br>Nguyo<br>s M. Ho | en<br>en<br>ess | 5    | 6     | TIT<br>MIC<br>FRE<br>SIL | LE<br>CROC<br>EQUE<br>ICON<br>3 NO. | DI<br>COL<br>CIRCI | LA LA<br>LUME<br>UIT, [<br>/ SYN | BUS,<br>DIGIT<br>NTHE | OHIO<br>FAL,<br>ESIZE | PHAER,       | RITIN<br>3218- | ME<br>3990<br>DETE | СТОІ   |  |

AMSC N/A 5962-V028-11

## 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance Phase detector/ Frequency synthesizer microcircuit, with an operating temperature range of -55°C to +125°C.

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer,s PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

V62/11607

01

X

B

Drawing number

Device type (See 1.2.1)

Case outline (See 1.2.2)

Lead finish (See 1.2.3)

1.2.1 Device type(s).

Device type

Generic

Circuit function

01

ADF4002-EP

Phase detector/ Frequency synthesizer

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

Outline letter

Number of pins

JEDEC PUB 95

Package style

X

16

JEDEC MO-153

Lead Thin Shrink Small Outline Package

1.2.3 <u>Lead finishes</u>. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

Finish designator

A Hot solder dip

B Tin-lead plate

C Gold plate

D Palladium

E Gold flash palladium

Z Other

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11607</b> |

|                       |      | REV            | PAGE 2           |

# 1.3 Absolute maximum ratings. 1/

| Voltage referenced :                                                          |                                             |

|-------------------------------------------------------------------------------|---------------------------------------------|

| AV <sub>DD</sub> to GND <u>2</u> /                                            | -0.3 V to +3.6 V                            |

| AV <sub>DD</sub> to DV <sub>DD</sub>                                          | -0.3 V to +0.3 V                            |

| V <sub>P</sub> to GND <u>2</u> /                                              | -0.3 V to +5.8 V                            |

| $V_P$ to $AV_{DD}$                                                            | -0.3 V to +5.8 V                            |

| Digital I/O voltage to GND 2/                                                 | $-0.3 \text{ V to DV}_{DD} + 0.3 \text{ V}$ |

| Analog I/O voltage to GND 2/                                                  | $-0.3 \text{ V to V}_P + 0.3 \text{ V}$     |

| REF <sub>IN</sub> , RF <sub>IN</sub> A, REF <sub>IN</sub> B to GND <u>2</u> / | -0.3 V to AV <sub>DD</sub> + 0.3 V          |

| Ambient operating temperature range                                           | -55°C to +125°C                             |

| Storage temperature range                                                     | -65°C to +150°C                             |

| Maximum junction temperature (T <sub>J</sub> )                                |                                             |

| Lead temperature, soldering:                                                  |                                             |

| Vapor phase (60 sec)                                                          | 215°C                                       |

| Infrared (15 sec)                                                             | 220°C                                       |

| Transistor count:                                                             |                                             |

| CMOS                                                                          | 6425                                        |

| Bipolar                                                                       | 303                                         |

## 2. APPLICABLE DOCUMENTS

JEDEC PUB 95 - Registered and Standard Outlines for Semiconductor Devices

(Applications for copies should be addressed to the Electronic Industries Alliance, North 10<sup>th</sup> St., Suite 240-S, Arlington, VA 22201-2107 or online at http://www.jedec.org)

#### 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|------|----------------|------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11607</b> |  |

|                       |      | REV            | PAGE 3           |  |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

<sup>2/</sup> GND = AGND = DGND = 0 V.

- 3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

- 3.5 <u>Diagrams</u>.

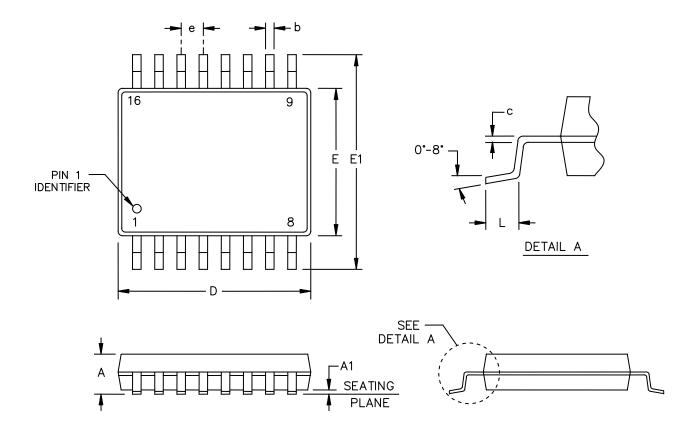

- 3.5.1 Case outline. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

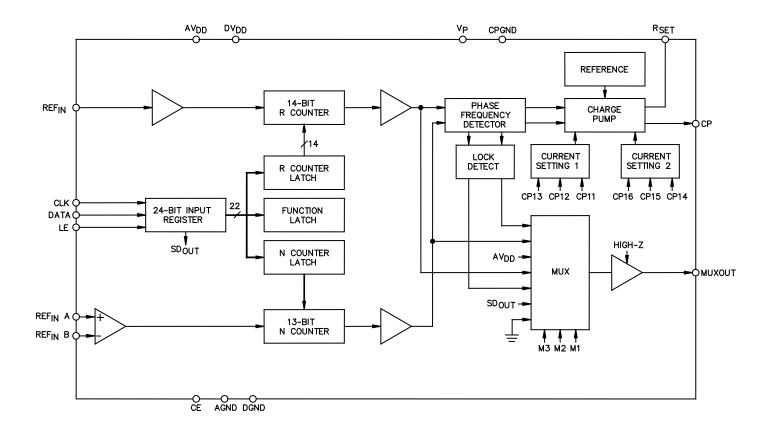

- 3.5.3 Functional block diagram. The functional block diagram shall be as shown in figure 3.

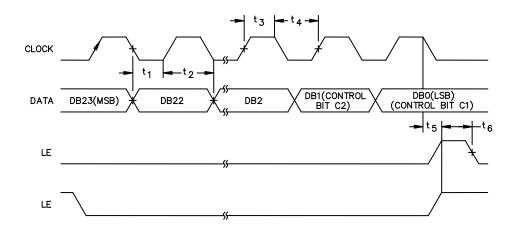

- 3.5.4 <u>Timing diagrams</u>. The timing diagrams shall be as shown in figure 4.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|----------|----------------|------------------|--|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/11607</b> |  |

|                       |          | REV            | PAGE 4           |  |

TABLE I. Electrical performance characteristics. 1/

| Test                                                             | Symbol                              | Test conditions                                                              | Limi             | ts      | Unit |

|------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------|------------------|---------|------|

|                                                                  |                                     | <u>2</u> /                                                                   | Min              | Max     |      |

|                                                                  |                                     | unless otherwise specified                                                   |                  |         |      |

| RF characteristics                                               |                                     | T                                                                            |                  |         |      |

| RF input sensitivity                                             |                                     |                                                                              | -10              | 0       | dBm  |

| RF Input frequency                                               | RF <sub>IN</sub>                    | For RF <sub>IN</sub> < 5 MHz, ensure slew rate (SR) > 4V/µs                  | 5                | 400     | MHz  |

| REF <sub>IN</sub> characteristics                                |                                     |                                                                              |                  |         |      |

| REF <sub>IN</sub> input frequency                                |                                     | For REF <sub>IN</sub> < 20 MHz, ensure SR > 50 V/µs                          | 20               | 300     | MHz  |

| REF <sub>IN</sub> input sensitivity 3/                           |                                     | Biased at AV <sub>DD</sub> /2 (ac coupling ensures AV <sub>DD</sub> /2 bias) | 8.0              | $AV_DD$ | Vp-p |

| REF <sub>IN</sub> input capacitance                              |                                     |                                                                              |                  | 10      | pF   |

| REF <sub>IN</sub> input current                                  |                                     |                                                                              |                  | ±100    | μΑ   |

| Phase Frequency detector                                         |                                     |                                                                              |                  |         |      |

| Phase detector frequency 4/                                      |                                     | ABP[2:1] = 00 (2.9 ns antibacklash pulse width)                              |                  | 104     | MHz  |

| Charge pump                                                      |                                     |                                                                              |                  |         |      |

| Sink/Source                                                      | I <sub>CP</sub>                     |                                                                              |                  |         |      |

| High value                                                       |                                     | $R_{SET} = 5.1 \text{ k}\Omega$                                              | 5 TY             | Έ       | mA   |

| Low value                                                        |                                     |                                                                              | 625 T            | YP      | μA   |

| Absolute accuracy                                                |                                     | $R_{SET} = 5.1 \text{ k}\Omega$                                              | 2.5 T            | ΥP      | %    |

| R <sub>SET</sub> range                                           |                                     |                                                                              | 3.0              | 11      | kΩ   |

| Three stage leakage                                              | I <sub>CP</sub>                     | T <sub>A</sub> = 25°C                                                        | 1 TY             | Έ       | nA   |

| I <sub>CP</sub> vs V <sub>CP</sub>                               |                                     | $0.5 \le V_{CP} \le (V_P - 0.5 \text{ V})$                                   | 1.5 T            | YP      | %    |

| Sink and source current matching                                 |                                     | $0.5 \le V_{CP} \le (V_P - 0.5 \text{ V})$                                   | 2 TY             |         | %    |

| I <sub>CP</sub> vs temperature                                   |                                     | $V_{CP} = V_P/2$                                                             | 2 TY             | Έ       | %    |

| Logic inputs                                                     | ·                                   | ,                                                                            |                  |         |      |

| Input high voltage                                               | V <sub>IH</sub>                     |                                                                              | 1.4              |         | V    |

| Input low voltage                                                | V <sub>IL</sub>                     |                                                                              |                  | 0.6     |      |

| Input current                                                    | I <sub>INH</sub> , I <sub>INL</sub> |                                                                              |                  | ±1      | μA   |

| Input capacitance                                                | Cin                                 |                                                                              |                  | 10      | pF   |

| Logic outputs                                                    |                                     |                                                                              |                  |         |      |

| Output high voltage                                              | V <sub>OH</sub>                     | Open-drain output, 1 kΩ pull up resistor to 1.8 V                            | 1.4              |         | V    |

| 3 1 1 3 1                                                        |                                     | CMOS output chosen                                                           | $V_{DD} - 0.4$   |         |      |

| Output high current                                              | I <sub>OH</sub>                     |                                                                              | 55               | 100     | μA   |

| Output low voltage                                               | V <sub>OL</sub>                     | I <sub>OL</sub> = 500 μA                                                     |                  | 0.4     | V    |

| Power supplies                                                   |                                     | 1 <del></del> - F                                                            | 1                |         |      |

| AV <sub>DD</sub>                                                 |                                     |                                                                              | 2.7              | 3.3     | V    |

| DV <sub>DD</sub>                                                 |                                     |                                                                              | AV <sub>DD</sub> |         | V    |

| V <sub>P</sub>                                                   |                                     | $AV_{DD} \le V_P \le 5.5 \text{ V}$                                          | AV <sub>DD</sub> | 5.5     | V    |

| I <sub>DD</sub> (AI <sub>DD</sub> +DI <sub>DD</sub> ) <u>5</u> / |                                     | 55 11 515 1                                                                  |                  | 6.0     | mA   |

| I <sub>P</sub>                                                   |                                     | T <sub>A</sub> = 25°C                                                        |                  | 0.4     | 1    |

| Power down mode                                                  |                                     | Alpp + Dlpp                                                                  | 1 TY             |         | μA   |

See footnotes at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11607</b> |

|                       |      | REV            | PAGE 5           |

TABLE I. Electrical performance characteristics - Continued.

| Test                                                      | Symb           | Test conditions                                | Limits               |     | Unit   |

|-----------------------------------------------------------|----------------|------------------------------------------------|----------------------|-----|--------|

|                                                           | ol             | 2/<br>unless otherwise specified               | Min                  | Max |        |

| Noise characteristics                                     |                |                                                |                      |     |        |

| Normalized phase noise floor (PN <sub>SYNTH</sub> ) 6/ 7/ |                | PLL loop BW = 500 kHz                          | -222 TYP<br>-122 TYP |     | dBc/Hz |

| Normalized 1/f Noise (PN <sub>1_f</sub> ) 6/ 8/           |                | Measured at 10 kHz offset, normalized to 1 GHz |                      |     |        |

| Timing characteristics 9/ 10/                             |                |                                                |                      |     |        |

| Data to clock setup time                                  | t <sub>1</sub> |                                                | 10                   |     | ns     |

| Data to clock hold time                                   | t <sub>2</sub> |                                                | 10                   |     |        |

| Clock high duration                                       | t <sub>3</sub> |                                                | 25                   |     |        |

| Clock low duration                                        | t <sub>4</sub> |                                                | 25                   |     |        |

| Clock to LE setup time                                    | <b>t</b> 5     |                                                | 10                   |     |        |

| LE pulse width                                            | t <sub>6</sub> |                                                | 20                   |     | 1      |

- Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- 2/ AV<sub>DD</sub> = DV<sub>DD</sub> = 3 V ±10%, AV<sub>DD</sub> ≤ V<sub>P</sub> ≤ 5.5 V, AGND = DGND = CPGND = 0 V, R<sub>SET</sub> = 5.1 kΩ, dBm referred to 50 Ω, -55°C ≤ T<sub>A</sub> ≤ +125°C, unless otherwise noted.

- 3/  $AV_{DD} = DV_{DD} = 3.0 V.$

- 4/ Guaranteed by design. Sample tested to ensure compliance.

- $\overline{5}$ /  $T_A = 25^{\circ}C$ ;  $AV_{DD} = DV_{DD} = 3 \text{ V}$ ;  $RF_{IN} = 350 \text{ MHz}$ . The current for any other setup (25°C, 3.0 V) in mA is given by 2.35 + 0.0046 (REF<sub>IN</sub>) + 0.0062 (RF); RF frequency and REF<sub>IN</sub> frequency in MHz.

- 6/ All phase noise measurements were performed with a Rohde&Schwarz FSU26 phase noise test system using the EVAL-ADF4002EBZ1 evaluation board and the ultralow noise, 100 MHz OCXO from Wenzel(Part No. 501-16843) as the PLL reference.

- The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20 log N (where N is the N divider value) and 10 log F<sub>PFD</sub>. PN<sub>SYTH</sub> = PN<sub>TOT</sub> 10 log F<sub>PFD</sub> 20 log N.

- The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency,  $f_{RF}$ , and at a frequency offset, f, is given by PN =  $P_{1,f}$  + 10log(10 kHz/f) + 20log( $f_{RF}$ /1 GHz).

- 9/ AV<sub>DD</sub> = DV<sub>DD</sub> = 3 V ±10%, AV<sub>DD</sub>  $\leq$  V<sub>P</sub>  $\leq$  5.5 V, AGND = DGND = CPGND = 0 V, R<sub>SET</sub> = 5.1 k $\Omega$ , dBm referred to 50  $\Omega$ ,  $-40^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  +85 $^{\circ}$ C, unless otherwise noted.

- 10/ Guaranteed by design, but not production tested.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|------|----------------|------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11607</b> |  |

|                       |      | REV            | PAGE 6           |  |

| Dimensions |        |             |    |             |      |  |  |  |  |

|------------|--------|-------------|----|-------------|------|--|--|--|--|

| Symbol     | Millim | Millimeters |    | Millimeters |      |  |  |  |  |

|            | Min    | Max         |    | Min         | Max  |  |  |  |  |

| Α          |        | 1.20        | Е  | 4.30        | 4.50 |  |  |  |  |

| A1         | 0.05   | 0.15        | E1 | 6.40 TYP    |      |  |  |  |  |

| b          | 0.19   | 0.30        | е  | 0.65 BSC    |      |  |  |  |  |

| С          | 0.09   | 0.20        | L  | 0.45        | 0.75 |  |  |  |  |

| D          | 4.90   | 5.10        |    |             | •    |  |  |  |  |

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|----------|----------------|------------------|--|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/11607</b> |  |

|                       |          | REV            | PAGE 7           |  |

|         | Case X             |         |          |  |  |  |  |  |  |

|---------|--------------------|---------|----------|--|--|--|--|--|--|

| Pin No. | Pin Name           | Pin No. | Pin Name |  |  |  |  |  |  |

| 1       | R <sub>SET</sub>   | 9       | DGND     |  |  |  |  |  |  |

| 2       | CP                 | 10      | CE       |  |  |  |  |  |  |

| 3       | CPGND              | 11      | CLK      |  |  |  |  |  |  |

| 4       | AGND               | 12      | DATA     |  |  |  |  |  |  |

| 5       | RF <sub>IN</sub> B | 13      | LE       |  |  |  |  |  |  |

| 6       | RF <sub>IN</sub> A | 14      | MUXOUT   |  |  |  |  |  |  |

| 7       | $AV_DD$            | 15      | $DV_DD$  |  |  |  |  |  |  |

| 8       | REFIN              | 16      | $V_P$    |  |  |  |  |  |  |

FIGURE 2. <u>Terminal connections</u>.

| Case X |                    |                                                                                                                                                                                                                                      |  |  |  |

|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PinNo. | Pin Name           | Description                                                                                                                                                                                                                          |  |  |  |

| 1      | R <sub>SET</sub>   | Connecting a resistor between this pin and CPGND sets the maximum charge pump output current. The nominal voltage potential at the $R_{\text{SET}}$ pin is 0.66 V. The relationship between $I_{\text{CP}}$ and $R_{\text{SET}}$ is: |  |  |  |

|        |                    | $I_{CP MAX} = \frac{25.5}{R_{SET}}$ So, with $R_{SET} = 5.1 \text{ k}\Omega$ , $I_{CP MAX} = 5 \text{ m}A$ .                                                                                                                         |  |  |  |

| 2      | CP                 | Charge Pump Output. When enabled, this provides ±l <sub>CP</sub> to the external loop filter, which in turn drives the external VCO.                                                                                                 |  |  |  |

| 3      | CPGND              | Charge Pump Ground. This is the ground return path for the charge pump.                                                                                                                                                              |  |  |  |

| 4      | AGND               | Analog Ground. This is the ground return path of the RF input.                                                                                                                                                                       |  |  |  |

| 5      | RF <sub>IN</sub> B | Complementary Input to the RF Input. This pin must be decoupled to the ground plane with a small bypass capacitor, typically 100 pF.                                                                                                 |  |  |  |

| 6      | RF <sub>IN</sub> A | Input to the RF Input. This small-signal input is ac-coupled to the external VCO.                                                                                                                                                    |  |  |  |

| 7      | $AV_{DD}$          | Analog Power Supply. This can range from 2.7 V to 3.3 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to the $AV_{DD}$ pin. $AV_{DD}$ must be the same value as $DV_{DD}$ .                |  |  |  |

| 8      |                    | Reference Input. This CMOS input has a nominal threshold of $AV_{DD}/2$ and a dc equivalent input resistance of 100 k $\Omega$ . This input can be driven from a TTL or CMOS crystal oscillator or it can be ac-coupled.             |  |  |  |

| 9      | DGND               | Digital Ground.                                                                                                                                                                                                                      |  |  |  |

| 10     | CE                 | Chip Enable. A logic low on this pin powers down the device and puts the charge pump output into three-state mode. Taking this pin high powers up the device, depending on the status of the Power-Down Bit PD1.                     |  |  |  |

| 11     | CLK                | Serial Clock Input. The serial clock is used to clock in the serial data to the registers. The data is latched into the 24-bit shift register on the CLK rising edge. This input is a high impedance CMOS input.                     |  |  |  |

| 12     | DATA               | Serial Data Input. The serial data is loaded MSB first; the two LSBs are the control bits. This input is a high impedance CMOS input.                                                                                                |  |  |  |

| 13     | LE                 | Load Enable. When LE goes high, the data stored in the shift registers is loaded into one of the four latches; the latch is selected using the control bits. This input is a high impedance CMOS input.                              |  |  |  |

| 14     | IVIOACOI           | Multiplexer Output. This output allows the lock detect, the scaled RF, or the scaled reference frequency to be accessed externally.                                                                                                  |  |  |  |

| 15     |                    | Digital Power Supply. This can range from 2.7 V to 3.3 V. Decoupling capacitors to the digital ground plane should be placed as close as possible to the $DV_{DD}$ pin. $DV_{DD}$ must be the same value as $AV_{DD}$ .              |  |  |  |

| 16     | $V_P$              | Charge Pump Power Supply. This should be greater than or equal to $AV_{DD}$ . In systems where $AV_{DD}$ is 3 V, $V_P$ can be set to 5.5 V and used to drive a VCO with a tuning voltage of up to 5 V.                               |  |  |  |

FIGURE 3. <u>Pin Function Descriptions</u>.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/11607</b> |

|                       |          | REV            | PAGE 8           |

FIGURE 3. Functional block diagram.

FIGURE 4. Timing diagram.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/11607</b> |

|                       |          | REV            | PAGE 9           |

#### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

# 5. PREPARATION FOR DELIVERY

- 5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

- 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item.

| Vendor item drawing administrative control number 1/ | Device<br>manufacturer<br>CAGE code | Vendor part number |

|------------------------------------------------------|-------------------------------------|--------------------|

| V62/11607-01XB                                       | 24355                               | ADF4002SRU-EP-RL7  |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

<u>CAGE code</u> <u>Source of supply</u>

24355 Analog Devices Rt 1 Industrial Park

PO Box 9106 Norwood, MA 02062

Point of contact: 7910 Triad Center Drive

Greensboro, NC 27409-9605

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/11607</b> |

|                       |      | REV            | PAGE 10          |