# **APE8968MP-3**

## **3A Ultra-low Dropout Regulator**

### Features

- Ultra-low Dropout of 0.23V (typical) at 3A Output Current

- Low ESR Output Capacitor (compatible with Multi-layer Chip Capacitors (MLCC))

- Reference Voltage of 0.8V

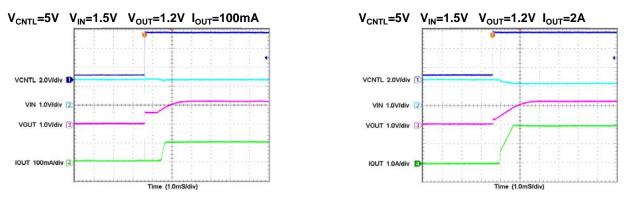

- Fast Transient Response

- Adjustable Output Voltage using External Resistors

- Power-On-Reset Monitoring on Both VCNTL and VIN Pins

- Internal Soft-Start

- Under-Voltage Protection

- Current-Limit and Thermal Shutdown Protection

- Power-OK Output with a Delay Time

- RoHS-compliant ESOP-8 Package, with Exposed

Pad halogen-free (HF) option available

### Description

The APE8968-3 is a 3A ultra low dropout linear regulator. This product is specifically designed to provide a supply voltage for front-side-bus termination on motherboards and NB applications. The IC needs two supply voltages, a control voltage for the circuitry and a main supply voltage for power conversion, to reduce power dissipation and provide extremely low dropout. The APE8968-3 integrates many functions. A Power-On-Reset (POR) circuit monitors both supply voltages to prevent incorrect operation. Thermal shutdown and current limit functions protect the device against thermal and current over-loads. A POK indicates the output status with a time delay which is set internally. It can control another converter for power sequencing. The APE8968 can be also be enabled by other power system. Pulling and holding the EN pin below 0.4V shuts off the output.

The APE8968-3 is available in an ESOP-8 package which features the small size of SO-8 with an exposed pad to reduce the junction-to-case thermal resistance, making it suitable for 2~3W applications.

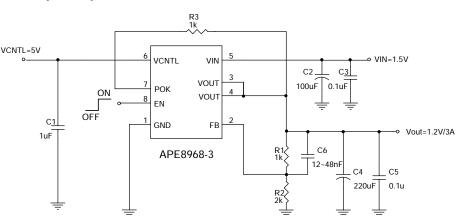

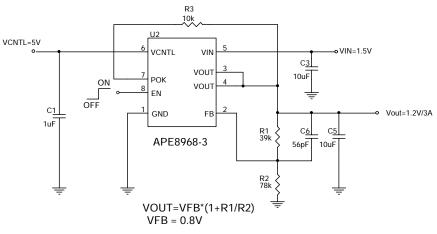

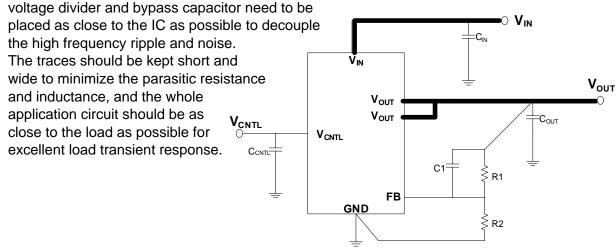

## **Typical Application Circuit**

### 1. Using an Output Capacitor with ESR $\geq 20 \text{m}\Omega$

### 2. Using an MLCC as the Output Capacitor

### Absolute Maximum Ratings (at T<sub>A</sub>=25°C)

| VCNTL Supply Voltage(V <sub>CNTL</sub> )                  | -0.3V to 7V                                |

|-----------------------------------------------------------|--------------------------------------------|

| VIN Supply Voltage(V <sub>IN</sub> )                      | -0.3V to 6V                                |

| EN and FB Pin Voltage(V $_{\rm I/O})$                     | -0.3V to $V_{CNTL}$ +0.3V                  |

| Power Dissipation(P <sub>D</sub> )                        | 3W                                         |

| Power Good Voltage(V <sub>POK</sub> )                     | -0.3V to 7V                                |

| Storage Temperature Range(T <sub>ST</sub> )               | -65°C to +150°C                            |

| Junction Temperature Range(T <sub>J</sub> )               | -40°C To 125°C                             |

| Operating Temperature Range (T <sub>OP</sub> )            | -40°C to +85°C                             |

| Thermal Resistance from Junction to $Case(Rth_{JC})$      | 15°C/W                                     |

| Thermal Resistance from Junction to Ambient( $Rth_{JA}$ ) | 40°C/W                                     |

| Note: Dth. is measured with the DCD segment eres (segment | ad to the eveneed and) of enarcy imptaly ( |

Note: Rth<sub>JA</sub> is measured with the PCB copper area (connected to the exposed pad) of approximately 1.5 in2 (Multi-layer)

### **Recommended Operating Conditions**

| VCNTL Supply Voltage(V <sub>CNTL</sub> ) | 3V to 5.5V                                                     |

|------------------------------------------|----------------------------------------------------------------|

| VIN Supply Voltage(V <sub>IN</sub> )     | 1.2V to 3.65V                                                  |

| Output Voltage(V <sub>OUT</sub> )        | 0.8V to $V_{IN}$ - $V_{DROP}$ ( $V_{CNTL}$ - $V_{OUT}$ > 1.9V) |

| Output Current(I <sub>OUT</sub> )        | 0 to 3A                                                        |

### **Ordering Information**

|                                   | Package Type                                                                                                                                                             |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APE8968MP-3TR<br>APE8968MP-HF-3TR | MP : RoHS-compliant ESOP-8                                                                                                                                               |

|                                   | MP-HF : RoHS-compliant halogen-free ESOP-8                                                                                                                               |

|                                   | Packing TR : Products in ESOP-8 are shipped on tape and reel.<br>The device is rated MSL3 for moisture sensitivity,<br>and the reel is packed in a moisture barrier bag. |

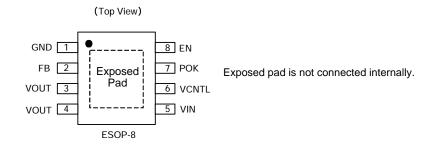

## **Pin Configuration**

THIS PRODUCT IS SENSITIVE TO ELECTROSTATIC DISCHARGE, PLEASE HANDLE WITH CAUTION.

USE OF THIS PRODUCT AS A CRITICAL COMPONENT IN LIFE SUPPORT OR OTHER SIMILAR SYSTEMS IS NOT AUTHORIZED. APEC DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. APEC RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN.

### **Pin Functional Description**

### FB

Connecting this pin to an external resistor divider provides the feedback voltage to the regulator. The output voltage set by the resistor divider is determined by:

$VOUT = 0.8 \times (1 + R1/R2)$

where R1 is connected from VOUT to FB with Kelvin sensing and R2 is connected from FB to GND. A bypass capacitor may be connected in parallel with R1 to improve load transient response. The recommended R2 and R1 are in the range of 1K~ $100k\Omega$ .

### VIN

Main supply input pin for power conversion. The voltage at this pin is monitored for Power-On Reset purposes.

### VCNTL

Power input pin of the control circuitry. Connecting this pin to a (recommended) +5V supply voltage provides the bias for the control circuitry. The voltage at this pin is also monitored for Power-On Reset purposes.

### POK

Power-OK signal output pin. This pin is an open-drain output used to indicate the status of the output voltage by sensing the FB voltage. This pin is pulled low when the rising FB voltage is not above the VPOK threshold or the falling FB voltage is below the VPOK threshold, indicating the output is not OK.

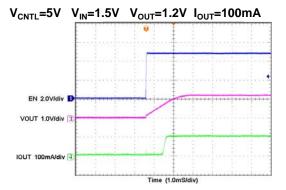

#### ΕN

Enable control pin. Pulling and holding this pin below 0.4V shuts down the output. When re-enabled, the IC undergoes a new soft-start cycle. If left open, this pin is internally pulled up to the VCNTL voltage, enabling the regulator.

### VOUT

Output of the regulator. Please connect Pin 3 and Pin 4 using wide tracks. It is essential to connect an output capacitor to this pin for closed-loop compensation and to improve the transient response.

## **Electrical Characteristics**

| $(V_{CNTL} = 5V, V_{IN} = 1.5V, V_{OUT} = 1.2V, T_A = 25^{\circ}C$ unless otherw | vise specified) |

|----------------------------------------------------------------------------------|-----------------|

| $(V_{CN1L} = 5V, V_{IN} = 1.5V, V_{OUI} = 1.2V, T_{A} = 25 O U IICS OUTCO$       | moe opeemeu)    |

| Parameter                   |                          | SYM                    | TEST CONDITION                                            |                                 | MIN   | TYP  | MAX   | UNITS |

|-----------------------------|--------------------------|------------------------|-----------------------------------------------------------|---------------------------------|-------|------|-------|-------|

| VCNTL POR Three             | shold                    | V <sub>CNTL</sub>      |                                                           |                                 | 2.5   | 2.7  | 2.9   | V     |

| VCNTL POR Hyste             | eresis                   | V <sub>CNTL(hys)</sub> |                                                           |                                 | -     | 0.4  | -     | V     |

| VIN POR Threshol            | ld                       | V <sub>IN</sub>        |                                                           |                                 | 0.8   | 0.9  | 1     | V     |

| VIN POR Hysteres            | sis                      | V <sub>IN(hys)</sub>   |                                                           |                                 | -     | 0.5  | -     | V     |

| VCNTL Nominal S             | upply Current            |                        | EN= V <sub>CNTL</sub>                                     |                                 | -     | 1    | 1.8   | mA    |

| VCNTL Shuntdown             | n Current                | I <sub>SD</sub>        | EN= 0V                                                    |                                 | -     | 15   | 30    | uA    |

| Feedback Voltage            |                          | $V_{FB}$               | V <sub>CNTL</sub> =3.0 ~ 5.5                              | V, I <sub>OUT</sub> =10mA       | 0.784 | 0.8  | 0.816 | V     |

| Load Regulation             |                          |                        | I <sub>OUT</sub> =0A ~ 3A                                 |                                 | -     | 0.2  | 0.5   | %     |

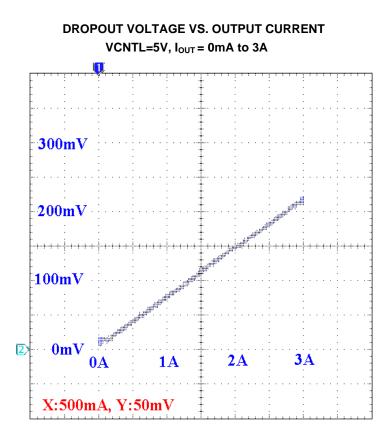

|                             |                          |                        |                                                           | 1.2V <v<sub>OUT&lt;1.8V</v<sub> | -     | 0.23 | 0.28  |       |

| Dropout Voltage             |                          | V <sub>DROP</sub>      |                                                           | $1.8V \leq V_{OUT} < 2.5V$      | -     | 0.24 | 0.29  | V     |

|                             |                          |                        |                                                           | $2.5V \leq V_{OUT} \leq 2.8V$   | -     | 0.28 | 0.38  | 1     |

| VOUT Pull Low Re            | esistance                |                        | EN=0V                                                     |                                 | -     | 65   | -     | Ω     |

| Soft Start Time             |                          | T <sub>SS</sub>        |                                                           |                                 | -     | 2    | 4     | ms    |

| EN Pin Logic High Threshold |                          | V <sub>ENH</sub>       | Enable                                                    |                                 | 1.2   | -    | -     | V     |

| Voltage                     |                          | $V_{\text{ENL}}$       | Disable                                                   |                                 | -     | -    | 0.4   | v     |

| EN Hysteresis               |                          |                        |                                                           |                                 | -     | 50   | -     | mV    |

| EN Pin Pull-Up Cu           | rrent                    | I <sub>EN</sub>        | EN=GND                                                    |                                 | -     | 10   | -     | uA    |

| Current Limit               |                          | I <sub>LIM</sub>       | V <sub>CNTL</sub> =3~5.5V<br>T <sub>J</sub> = -40 ~ 125°C |                                 | 4.3   | -    | -     | А     |

|                             |                          | LIM                    |                                                           |                                 |       |      |       |       |

| Ripple Rejection            | Rejection VIN PSRR F=120 |                        | F=120Hz lour=                                             | =120Hz, I <sub>OUT</sub> =100mA |       | 65   | -     | dB    |

| VCNTL                       |                          |                        |                                                           | -                               | 65    | -    |       |       |

| Under-Voltage Thr           | reshold                  |                        | VFB Falling                                               |                                 | -     | 0.4  | -     | V     |

| POK Threshold Volt          |                          | V <sub>POK</sub>       | VFB Rising                                                |                                 | 89%   | 92%  | 95%   | VFB   |

| POK Threshold Vo<br>Not OK  | ltage for Power          | V <sub>PNOK</sub>      | VFB Falling                                               |                                 | 79%   | 82%  | 85%   | VFB   |

| POK Low Voltage             |                          |                        | POK sinks 5mA                                             |                                 | -     | 0.25 | 0.4   | V     |

| POK Delay Time              |                          | T <sub>DELAY</sub>     |                                                           |                                 | 0.8   | 2    | 4     | ms    |

| Thermal Shutdown            | Temp                     | TSD                    |                                                           |                                 | -     | 150  | -     | °C    |

| Thermal Shutdown Hysteresis |                          |                        |                                                           |                                 | -     | 50   | -     | Ŭ     |

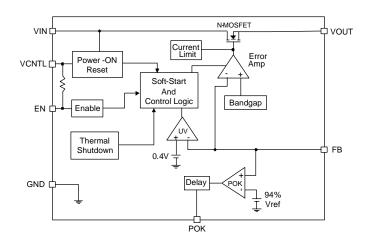

## **Block Diagram**

### **Function Descriptions**

#### **Power-On-Reset**

A Power-On-Reset (POR) circuit monitors both input voltages at VCNTL and VIN pins to prevent incorrect logic controls. The POR function initiates a soft-start process after the two supply voltages exceed their rising POR threshold voltages during powering on. The POR function also pulls low the POK pin regardless of the output voltage when the VCNTL voltage falls below its falling POR threshold.

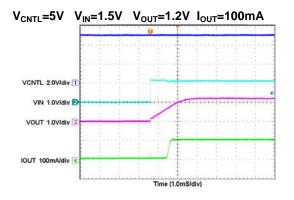

#### **Internal Soft-Start**

An internal soft-start function controls the slew rate of the output voltage to limit the current surge at start-up. The typical soft-start interval is about 2ms.

#### **Current Limit**

The APE8968-3 monitors the current via the output NMOSFET and limits the maximum current to prevent damage to the load and the APE8968-3 during overload or short circuit conditions.

#### **Output Voltage Regulation**

An error amplifier working with a temperature compensated 0.8V reference and an output NMOSFET regulates output to the preset voltage. The error amplifier is designed with high bandwidth and DC gain, providing very fast transient response and less load regulation. It compares the reference with the feedback voltage and amplifies the difference to drive the output NMOSFET which provides load current from VIN to VOUT.

#### **Under Voltage Protection (UVP)**

The APE8968-3 monitors the voltage on the FB pin after the soft-start process is finished. Therefore the UVP is disabed during soft-start. When the voltage on FB pin falls below the under-voltage threshold, the UVP circuit shuts off the output immediately. After a while, the APE8968-3 starts a new soft-start to regulate output.

#### **Thermal Shutdown**

A thermal shutdown circuit limits the junction temperature of the APE8968-3. When the junction temperature exceeds +150°C, a thermal sensor turns off the output NMOSFET, allowing the device to cool down. The regulator regulates the output again through the initiation of a new soft-start cycle after the junction temperature cools by 50°C, resulting in pulsed output during continuous thermal overload conditions.

### **PCB Layout Consideration**

It is necessary to solder the exposed pad to either Vin or the Gnd plane as a heat sink and ensure it has enough pcb copper area to radiate the heat. Input capacitor, output capacitor,

### **Typical Performance Characteristics**

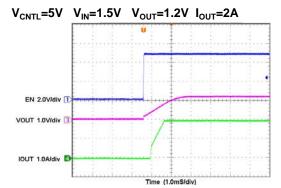

#### START UP WAVEFORM -1 VCNTL READY

V<sub>CNTL</sub>=5V V<sub>IN</sub>=1.5V V<sub>OUT</sub>=1.2V I<sub>OUT</sub>=1A VCNTL 2.0V/div 🔳 VIN 1.0V/div VOUT 1.0V/div 3 IOUT 1.0A/div Time (1.0mS/div)

START UP WAVEFORM -2 VIN READY

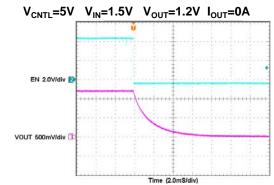

EN OFF  $\rightarrow$  ON

## **TYPICAL PERFORMANCE CHARACTERISTICS**

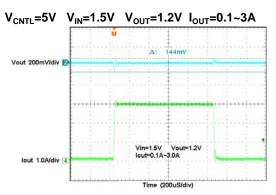

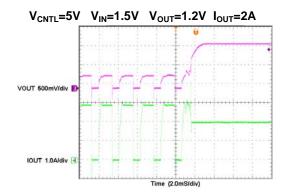

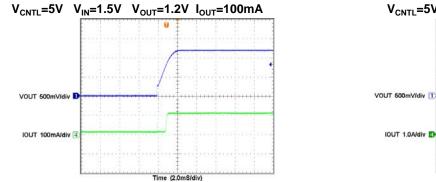

LOAD TRANSIENT

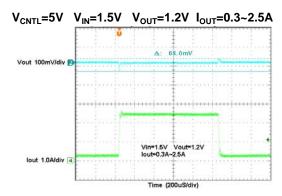

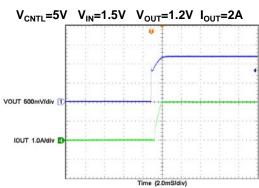

SHORT CIRCUIT RELEASE

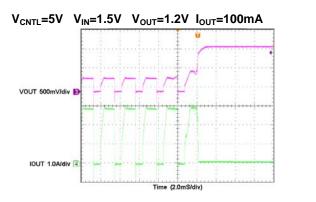

#### THERMAL SHUT DOWN RELEASE

## **TYPICAL PERFORMANCE CHARACTERISTICS**

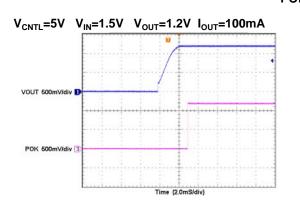

POK VS. DISABLE V<sub>CNTL</sub>=5V V

©2009 Advanced Power Electronics Corp. USA www.a-powerusa.com

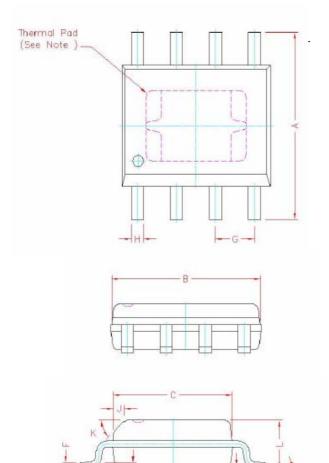

## Package Dimensions: ESOP-8

|         | Millimeters |      |      |  |  |

|---------|-------------|------|------|--|--|

| SYMBOLS | MIN         | NOM  | MAX  |  |  |

| А       | 5.80        | 6.00 | 6.20 |  |  |

| В       | 4.80        | 4.90 | 5.00 |  |  |

| С       | 3.80        | 3.90 | 4.00 |  |  |

| D       | 0°          | 4°   | 8°   |  |  |

| Е       | 0.40        | 0.65 | 0.90 |  |  |

| F       | 0.19        | 0.22 | 0.25 |  |  |

| М       | 0.00        | 0.08 | 0.15 |  |  |

| Н       | 0.35        | 0.42 | 0.49 |  |  |

| L       | 1.35        | 1.55 | 1.75 |  |  |

| J       | 0.375 REF.  |      |      |  |  |

| К       | 45°         |      |      |  |  |

| G       | 1.27 TYP.   |      |      |  |  |

### NOTES:

(L/F 90\*90) Thermal Pad Dimensions □2.25 ±0.1

1. All dimensions are in millimeters.

2. Dimensions do not include mold protrusions.

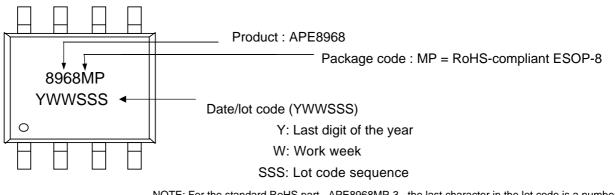

### **Marking Information**

NOTE: For the standard RoHS part, APE8968MP-3, the last character in the lot code is a number. For the halogen-free option, APE8968MP-HF-3, the last character is a letter.