|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      | I                 |      |                        | 1    |        |        |        |        |

|--------------------|-----------------------|----------|--------|---------|---------------|--------|--------|-----|-------------------------------------------------------------------------------------------|----|-------|-------------|------|-------------------|------|------------------------|------|--------|--------|--------|--------|

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

| Prepared           | in accord             | lance wi | th ASN | /IE Y14 | 1.24          |        |        |     |                                                                                           |    |       |             |      |                   |      |                        | Ve   | ndor i | tem dı | rawing | J      |

| REV                |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

| PAGE               |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

| REV                |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

| PAGE               |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

| REV STA<br>OF PAGE |                       | RE       |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        |        |        |        |

|                    |                       | PAG      |        | PARE    | 1<br>0 8 V    | 2      | 3      | 4   | 5                                                                                         | 6  |       |             |      |                   |      |                        |      |        |        |        |        |

| PMIC N/A           | A                     |          |        |         | Phu H. Nguyen |        |        |     | DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990<br>http://www.landandmaritime.dla.mil/ |    |       |             |      |                   |      |                        |      |        |        |        |        |

| Original d<br>Yነ   | ate of dra<br>Y MM DD | awing    | CHE    | CKED    |               | hu H.  | Nguy   | en  |                                                                                           |    | TIT   |             |      | . II <del>T</del> |      | TAI                    |      |        |        |        |        |

| 13-04-09           |                       | APP      | ROVE   |         |               | 6 M. H | ess    |     |                                                                                           | UV | /OV F | POSI        | TIVE | /NEG              | )ATI | LINE<br>/E VC<br>IIC S | DLTA | GE     |        |        |        |

|                    |                       |          | SI     | ZE      | COD           | E IDE  | INT. N | 0.  |                                                                                           |    | DW    | g no.       |      |                   |      |                        |      |        |        |        |        |

|                    |                       |          | 4      | 4       |               |        | 16     | 236 |                                                                                           |    |       |             |      |                   | /62  | 2/12                   | 265  | 5      |        |        |        |

|                    |                       |          | REV    | ,       |               |        |        |     |                                                                                           |    | PAC   | <b>BE</b> 1 | OF   | 11                |      |                        |      |        |        |        |        |

| AMSC N/A           |                       |          |        |         |               |        |        |     |                                                                                           |    |       |             |      |                   |      |                        |      |        | 5      | 962-V  | 061-13 |

REVISIONS

DESCRIPTION

DATE

APPROVED

LTR

## 1. SCOPE

1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance quad UV/OV Positive/Negative voltage supervisor microcircuit, with an operating temperature range of -55°C to +125°C.

1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| V62/12655<br>Drawing<br>number | - <u>01</u><br>Device type<br>(See 1.2.1) | Case outline<br>(See 1.2.2) | Lead finish<br>(See 1.2.3)           |

|--------------------------------|-------------------------------------------|-----------------------------|--------------------------------------|

| 1.2.1 Device type(s).          |                                           |                             |                                      |

| Device type                    | <u>Generic</u>                            | <u>Cir</u>                  | cuit function                        |

| 01                             | ADM2914-EP                                | Quad UV/OV                  | Positive/Negative voltage supervisor |

1.2.2 <u>Case outline(s)</u>. The case outlines are as specified herein.

| Outline letter | Number of pins | JEDEC PUB 95    | Package style                |

|----------------|----------------|-----------------|------------------------------|

| Х              | 16             | JEDEC MO-137-AB | Shrink Small Outline Package |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator          | Material                                                                                     |

|----------------------------|----------------------------------------------------------------------------------------------|

| A<br>B<br>C<br>D<br>E<br>Z | Hot solder dip<br>Tin-lead plate<br>Gold plate<br>Palladium<br>Gold flash palladium<br>Other |

|                            |                                                                                              |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12655</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | 16236          |                          |

|                       |      | REV            | PAGE 2                   |

### 1.3 Absolute maximum ratings. 1/

| V <sub>CC</sub>                                        |                                     |

|--------------------------------------------------------|-------------------------------------|

| Timer                                                  | -0.3 V to (V <sub>CC</sub> + 0.3 V) |

| VL <sub>X</sub> , VH <sub>X</sub> , <u>LATCH</u> , SEL | -0.3 V to +7.5 V                    |

| I <sub>CC</sub>                                        | 10 mA                               |

| Reference load current (I <sub>REF</sub> )             | ±1 mA                               |

| $I_{\overline{UV}}, I_{\overline{OV}}$                 | 10 mA                               |

| Operating temperature range:                           | -55°C to +125°C                     |

| Storage temperature range                              | -65°C to 150°C                      |

| Lead temperature (Soldering, 10 sec)                   | 300°C                               |

## 1.4 Thermal characteristics.

Thermal resistance

| Case outline | $\theta_{JA}$ | Unit |

|--------------|---------------|------|

| Case X       | 104           | °C/W |

### 2. APPLICABLE DOCUMENTS

JEDEC – SOLID STATE TECHNOLOGY ASSOCIATION (JEDEC)

## JEP95 – Registered and Standard Outlines for Semiconductor Devices

(Copies of these documents are available online at http://www.jedec.org or from JEDEC – Solid State Technology Association, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201.)

## 3. REQUIREMENTS

3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

<u>1</u>/ Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12655</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |  |

|                       |      | REV            | PAGE 3                   |  |

## 3.5 Diagrams.

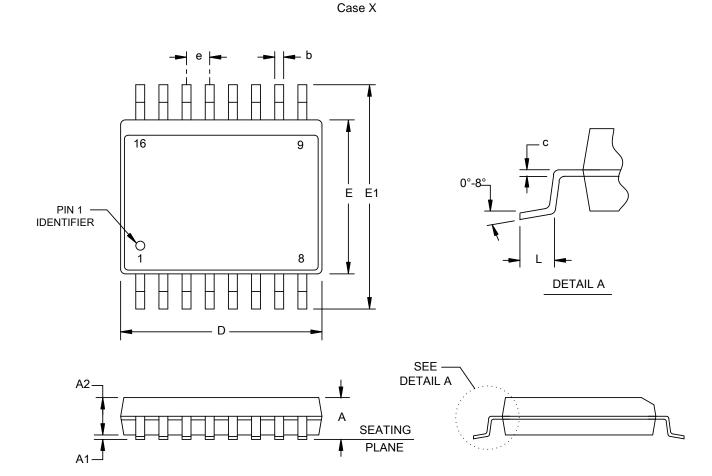

- 3.5.1 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

- 3.5.3 <u>Terminal function</u>. The terminal function shall be as shown in figure 3.

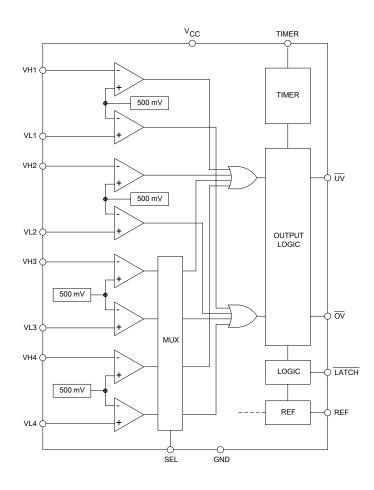

- 3.5.4 <u>Functional block diagram</u>. The functional block diagram shall be as shown in figure 4.

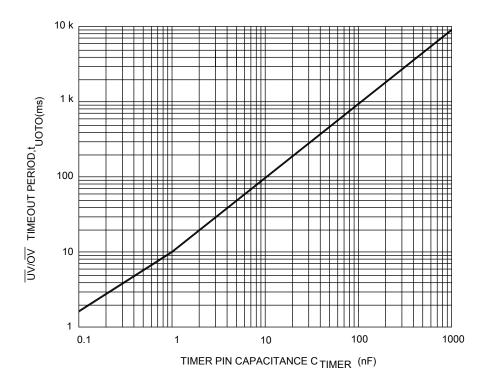

- 3.5.5  $\underline{UV}/\overline{OV}$  Timeout period vs Capacitance. The  $\overline{UV}/\overline{OV}$  Timeout period vs Capacitance shall be as shown in figure 5.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12655</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV            | PAGE 4                   |

## TABLE I. <u>Electrical performance characteristics</u>. <u>1</u>/

| Test                                            | Symbol                                                             | Test conditions                                                              | Limits |      |                    |          |  |

|-------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------|--------|------|--------------------|----------|--|

|                                                 |                                                                    | <u>2</u> /                                                                   | Min    | Тур  | Max                |          |  |

| Shunt regulator                                 |                                                                    |                                                                              |        |      |                    |          |  |

| V <sub>CC</sub> shunt regulator voltage         | V <sub>SHUNT</sub>                                                 | $I_{CC} = 5 \text{ mA}$                                                      | 6.2    | 6.6  | 6.9                | V        |  |

|                                                 | V SHUNT                                                            | $T_A = -55^{\circ}C$ to $+125^{\circ}C$                                      | 6.2    | 6.6  | 7.0                | V        |  |

| V <sub>CC</sub> shunt regulator load regulation | $\Delta V_{SHUNT}$                                                 | $I_{CC} = 2 \text{ mA to } 10 \text{ mA}$                                    |        | 200  | 300                | m\       |  |

| Supply                                          |                                                                    |                                                                              |        |      |                    |          |  |

| Supply voltage <u>3/</u>                        | V <sub>CC</sub>                                                    |                                                                              | 2.3    |      | V <sub>SHUNT</sub> | V        |  |

| Minimum VCC output valid                        | V <sub>CCR(MIN)</sub>                                              |                                                                              |        |      | 1                  |          |  |

| Supply under voltage lockout                    | V <sub>CC(UVLO)</sub>                                              | V <sub>CC</sub> rising                                                       | 1.9    | 2    | 2.1                |          |  |

| Supply under voltage lockout hysteresis         | $\Delta V_{CC(HYST)}$                                              |                                                                              | 5      | 25   | 50                 | m\       |  |

| Supply current                                  | lcc                                                                | $V_{CC} = 2.3 \text{ V}$ to 6 V                                              |        | 62   | 100                | μA       |  |

| Reference output                                |                                                                    |                                                                              |        |      |                    |          |  |

| Reference output voltage                        | V <sub>REF</sub>                                                   | $I_{VREF} = \pm 1 \text{ mA}$                                                | 0.985  | 1    | 1.015              | V        |  |

| Reference earpar voltage                        | ▼ REF                                                              | T <sub>A</sub> = -55°C to +125°C                                             | 0.985  | 1    | 1.020              | <u> </u> |  |

| Undervoltage/Overvoltage characteristic         |                                                                    |                                                                              |        |      |                    |          |  |

| Undervoltage/Overvoltage threshold              | V <sub>UOT</sub>                                                   |                                                                              | 492.5  | 500  | 507.5              | m١       |  |

| Undervoltage/Overvoltage threshold to           | t <sub>UOD</sub>                                                   | $VHx = V_{UOT} - 5 \text{ mV}$ or                                            | 50     | 125  | 500                | με       |  |

| output delay                                    |                                                                    | $VLx = V_{UOT} + 5 mV$                                                       |        |      |                    |          |  |

| VHx, VLx input current                          | IVHL                                                               |                                                                              |        |      | ±15                | nA       |  |

|                                                 | •vnL                                                               | $T_{A} = -55^{\circ}C \text{ to } +125^{\circ}C$                             |        |      | ±30                |          |  |

| UV/OV timeout period                            | tuoтo                                                              | C <sub>TIMER</sub> = 1 nF                                                    | 6      | 8.5  | 12.5               |          |  |

|                                                 | 0010                                                               | $T_A = -55^{\circ}C$ to $+125^{\circ}C$                                      | 6      | 8.5  | 14                 |          |  |

| OV Latch clear input                            |                                                                    |                                                                              |        |      |                    |          |  |

| OV Latch clear threshold input high             | V <sub>LATCH(IH)</sub>                                             |                                                                              | 1.2    |      |                    | V        |  |

| 0V Latch clear threshold input low              | V <sub>LATCH(IL)</sub>                                             |                                                                              |        |      | 0.8                |          |  |

| LATCH input current                             | ILATCH                                                             | V <sub>LATCH</sub> >0.5 V                                                    |        |      | ±1                 | μA       |  |

| Timer characteristics                           |                                                                    | LATCH                                                                        |        |      |                    |          |  |

|                                                 |                                                                    | V <sub>TIMER</sub> = 0 V                                                     | -1.3   | -2.1 | -2.8               | μA       |  |

| Timer pull up current                           | TIMER(UP)                                                          | $T_{A} = -55^{\circ}C \text{ to } +125^{\circ}C$                             | -1.2   | -2.1 | -2.8               | •        |  |

|                                                 |                                                                    | $V_{\text{TIMER}} = 1.6 \text{ V}$                                           | 1.3    | 2.1  | 2.8                |          |  |

| Timer pull down current                         | ITIMER(DOWN)                                                       | $T_{A} = -55^{\circ}C \text{ to } +125^{\circ}C$                             | 1.2    | 2.1  | 2.8                |          |  |

| Timer disable voltage                           | V <sub>TIMER(DIS)</sub>                                            | Reference to V <sub>CC</sub>                                                 | -180   | -270 |                    | ۳        |  |

| Output voltage                                  | • TIMER(DIS)                                                       |                                                                              | 100    | 210  |                    |          |  |

| Output voltage high                             | $\overline{\rm UV}/\overline{\rm OV},{\rm V}_{\rm OH}$             | $V_{CC} = 2.3 \text{ V}; I_{\overline{UV}/\overline{OV}} = -1 \ \mu\text{A}$ | 1      |      |                    | V        |  |

|                                                 |                                                                    | $V_{CC} = 2.3 \text{ V}; I_{\overline{UV}/\overline{OV}} = -2.5 \text{ mA}$  | -      | 0.1  | 0.3                |          |  |

| Output voltage low                              | $\overline{\text{UV}}/\overline{\text{OV}},  \text{V}_{\text{OL}}$ | $V_{CC} = 1 \text{ V}; I_{\overline{UV}} = -100 \mu\text{A}$                 |        | 0.01 | 0.15               |          |  |

| Three state input SEL                           |                                                                    |                                                                              |        | 0.01 | 0.10               |          |  |

| Low level input voltage                         | VIL                                                                |                                                                              |        |      | 0.4                | V        |  |

| High level input voltage                        | VIL                                                                |                                                                              | 1.4    |      |                    |          |  |

| Pin voltage when left in high-Z state           | Vz                                                                 | $I_{SEL} = \pm 10 \ \mu A$                                                   | 0.7    | 0.9  | 1.1                |          |  |

| 5 5 5                                           | -                                                                  | $T_{A} = -55^{\circ}C \text{ to } +125^{\circ}C$                             | 0.6    | 0.9  | 1.2                |          |  |

| SEL high, low input current                     | I <sub>SEL</sub>                                                   |                                                                              |        |      | ±25                | μA       |  |

| Maximum SEL input current                       | I <sub>SEL(MAX)</sub>                                              | SEL tied to V <sub>CC</sub> or GND                                           |        |      | ±30                | ۳,       |  |

See footnote at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/12655 |

|                       |      | REV            | PAGE 5    |

TABLE I. Electrical performance characteristics - Continued. 1/

- 1/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- 2'  $-55^{\circ}C \le T_A \le +125^{\circ}C$ . Typical values at  $T_A = 25^{\circ}C$ , unless otherwise noted.  $V_{CC} = 3.3 \text{ V}$ ,  $VL_X = 0.45 \text{ V}$ ,  $VH_X = 0.55 \text{ V}$ ,  $\overline{LATCH} = V_{CC}$ , SEL =  $V_{CC}$ , unless otherwise noted.

- 3/ The maximum voltage on the V<sub>CC</sub> pin is limited by the input current. The V<sub>CC</sub> pin has an internal 6.5 V shunt regulator and, therefore, a low impedance supply greater than 6 V may exceed the maximum allowed input current. When operating from a higher supply then 6 V, always use a dropper resistor.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12655</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |  |

|                       |      | REV            | PAGE 6                   |  |

|        | Dimensions |      |             |      |        |        |      |             |       |

|--------|------------|------|-------------|------|--------|--------|------|-------------|-------|

| Symbol | Inches     |      | Millimeters |      | Symbol | Inches |      | Millimeters |       |

|        | Min        | Max  | Min         | Max  |        | Min    | Max  | Min         | Max   |

| А      | .053       | .069 | 1.35        | 1.75 | D      | .189   | .197 | 4.80        | 5.00  |

| A1     | .049       | .065 | 1.25        | 1.65 | E      | .150   | .158 | 3.81        | 4.01  |

| A2     | .004       | .010 | 0.10        | 0.25 | E1     | .228   | .244 | 5.79        | 6.20  |

| b      | .008       | .012 | 0.20        | 0.30 | е      | .025   | BSC  | 0.64        | 4 BSC |

| С      | .006       | .010 | 0.15        | 0.25 | L      | .041   | REF  | 1.04        | 4 REF |

## NOTES:

1. Controlling dimensions are in inches; millimeters dimensions are rounded off inch; equivalents for reference only and are not appropriate for use in design.. Falls within JEDEC MO-137-AB.

2.

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | 16236          | V62/12655 |

|                       |      | REV            | PAGE 7    |

|                    | Case outline X     |                    |                          |  |  |  |

|--------------------|--------------------|--------------------|--------------------------|--|--|--|

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol       |  |  |  |

| 1                  | VH1                | 16                 | Vcc                      |  |  |  |

| 2                  | VL1                | 15                 | TIMER                    |  |  |  |

| 3                  | VH2                | 14                 | SEL                      |  |  |  |

| 4                  | VL2                | 13                 | LATCH                    |  |  |  |

| 5                  | VH3                | 12                 | $\overline{\mathrm{UV}}$ |  |  |  |

| 6                  | VL3                | 11                 | $\overline{\text{OV}}$   |  |  |  |

| 7                  | VH4                | 10                 | REF                      |  |  |  |

| 8                  | VL4                | 9                  | GND                      |  |  |  |

FIGURE 2. <u>Terminal connections</u>.

|                    | Case outline X           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|--------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Terminal<br>number | Mnemonic                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 1                  | VH1                      | Voltage High Input 1 and Voltage High Input 2. If the voltage monitored by VH1 or VH2 drops below                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 3                  | VH2                      | 0.5 V, an undervoltage condition is detected. Connect to V <sub>CC</sub> when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 2                  | VL1                      | Voltage Low Input 1 and Voltage Low Input 2. If the voltage monitored by VL1 or VL2 rises above                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 4                  | VL2                      | 0.5 V, an overvoltage condition is detected. Tie to GND when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 5                  | VH3                      | Voltage High Input 3 and Voltage High Input 4. The polarity of these inputs is determined by the state of the SEL pin. When the monitored input is configured as a positive voltage and the voltage                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 7                  | VH4                      | monitored by VH3 and VH4 drops below 0.5 V, an undervoltage condition is detected. Conversely, when the input is configures as a negative voltage and the inputs drops below 0.5 V, an overvoltage condition is detected. Connect to $V_{CC}$ when not in use.                                                                                                                                                                                                                                            |  |  |  |  |

| 6                  | VL3                      | Voltage Low Input 3 and Voltage Low Input 4. The polarity of these inputs is determined by the state of the SEL pin. When the monitored input is configured as a positive voltage and the voltage monitored by VL3 and VL4 rises above 0.5 V, an overrvoltage condition is detected. Conversely, when                                                                                                                                                                                                     |  |  |  |  |

| 8                  | VL4                      | the input is configures as a negative voltage and the inputs rises above 0.5 V, an undervoltage condition is detected. Tie to GND when not in use.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 9                  | GND                      | Device Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 10                 | REF                      | Buffered Reference Output. This pin is a 1 V reference that is used as an offset when monitoring negative voltages. This pin can source ro sink 1 mA and drive loads up to 1 nF. Larger capacitive loads may lead to instability. Leave unconnected when not in use.                                                                                                                                                                                                                                      |  |  |  |  |

| 11                 | $\overline{\mathrm{OV}}$ | Overvoltage Reset output. $\overline{OV}$ is asserted low if a negative polarity input voltage drops below its associated threshold or if a positive polarity input voltage exceeds its threshold. This device allows . $\overline{OV}$ to be latched low. This pin has a weak pull up to V <sub>CC</sub> and can be pulled up to 16 V externally. Leave this pin unconnected when not in use.                                                                                                            |  |  |  |  |

| 12                 | ŪV                       | Undervoltage Reset Output $\overline{UV}$ is asserted low if a negative polarity input voltage exceeds its associated threshold or if a positive polarity input voltage drops below its threshold. $\overline{UV}$ is held low for an adjustable time out period set by the external capacitor tied to the TIMER pin. The $\overline{UV}$ pin has a weak pull up to V <sub>CC</sub> and can be pulled up to 16 V externally via an external pull up resistor. Leave this pin unconnected when not in use. |  |  |  |  |

FIGURE 3. Terminal function.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | 16236          | V62/12655 |

|                       |      | REV            | PAGE 8    |

|                    | Case outline X – Continued. |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|--------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Terminal<br>number | Mnemonic                    | Description                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 13                 | LATCH                       | $\overline{\text{OV}}$ Latch Bypass Input/Clear Pin. When pulled high, the $\overline{\text{OV}}$ latch is cleared. When held high, the $\overline{\text{OV}}$ output has the same delay and output characteristics as the $\overline{\text{UV}}$ output. When pulled low, the $\overline{\text{OV}}$ output is latched when asserted.                                         |  |  |  |  |

| 14                 | SEL                         | Input Polarity Select. This three state input pin allows the polarity of VH3, VL3, VH4 and VL4 to be configured. Connect to VCC or GND, or leave open to select one of three possible input polarity configurations.                                                                                                                                                           |  |  |  |  |

| 15                 | TIMER                       | Adjustable Reset Delay Timer. Connect an external capacitor to the TIMER pin to program the reset timeout delay. Refer to FIGURE 5. Connect this pin to $V_{CC}$ to bypass the timer.                                                                                                                                                                                          |  |  |  |  |

| 16                 | V <sub>CC</sub>             | Supply Voltage. VCC operates as a direct supply for voltages up to 6 V. For voltages greater than 6 V, it operates as a shunt regulator. A dropper resistor must be used in this configuration to limit the current to less than 10 mA. When used without the resistor, the voltage at this pin must not exceed 6 V. A 0.1 $\mu$ F bypass capacitor or greater should be used. |  |  |  |  |

# FIGURE 3. <u>Terminal function</u> - Continued.

FIGURE 4. Functional block diagram

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12655</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |  |

|                       |      | REV            | PAGE 9                   |  |

FIGURE 5. UV/OV Timeout period vs Capacitance.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12655</b> |

|-----------------------|------|----------------|--------------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   |                          |

|                       |      | REV            | PAGE 10                  |

### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

## 5. PREPARATION FOR DELIVERY

5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

### 6. NOTES

6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <u>http://www.landandmaritime.dla.mil/Programs/Smcr/</u>.

| Vendor item drawing<br>administrative control<br>number <u>1</u> / | Device<br>manufacturer<br>CAGE code | Vendor part number |

|--------------------------------------------------------------------|-------------------------------------|--------------------|

| V62/12655-01XE                                                     | 24355                               | ADM2914-1SRQZEP-R7 |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

#### CAGE code

24355

Source of supply

Analog Devices 1 Technology Way P.O. Box 9106 Norwood, MA 02062-9106

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. <b>V62/12655</b> |  |

|-----------------------|------|----------------|--------------------------|--|

| COLUMBUS, OHIO        | A    | 16236          |                          |  |

|                       |      | REV            | PAGE 11                  |  |