|          |                         |          |                                                |                          |        |        |     |      |       |                       | REVIS | SIONS  |      |       |       |       |               |        |       |     |

|----------|-------------------------|----------|------------------------------------------------|--------------------------|--------|--------|-----|------|-------|-----------------------|-------|--------|------|-------|-------|-------|---------------|--------|-------|-----|

|          |                         |          |                                                | LTR                      |        |        |     | DESC | RIPTI | ON                    |       |        |      | D     | ATE   |       | A             | APPRO  | OVED  |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

| Prepared | d in accord             | ance wit | th ASME                                        | Y14.24                   |        |        |     |      |       |                       |       |        |      |       |       | Ve    | ndor it       | tem dr | awing |     |

| REV      |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        | Π     |     |

| PAGE     |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

| REV      |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

| PAGE     |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

| REV ST   | ATUE                    | REV      | <u>                                       </u> |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

| OF PAG   |                         | PAG      |                                                | 1                        | 2      | 3      | 4   | 5    | 6     | 7                     | 8     | 9      | 10   | 11    | 12    | 13    | 14            | 15     | 16    |     |

| PMIC N/  | /A                      |          | PREPA                                          | RED BY                   | ,      |        |     |      |       | DLA LAND AND MARITIME |       |        |      |       |       |       |               |        |       |     |

|          |                         |          | RICK                                           | OFFICE                   | R      |        |     |      |       |                       | •     | COL    | LUME | BUS,  | OHI   | O 43  | 218-          | 3990   |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       | ttp:// | www  | .lanc | landı | narit | ime.          | dla.m  | iil/  |     |

|          | date of dra<br>'Y-MM-DD |          | CHECK<br>RAJES                                 | <b>(ED BY</b><br>SH PITH | ADIA   |        |     |      |       | TIT                   |       |        |      |       |       |       |               |        |       |     |

|          | 12-11-19                |          | APPRO                                          | VED BY                   | ,      |        |     |      |       |                       |       |        |      |       |       |       | AR, 1<br>GITA |        | ANN   | EL, |

|          |                         | CHAR     | LES F. S                                       | SAFFL                    | .E     |        |     |      | CO    | NVE                   | RTEF  |        |      |       |       |       |               | LITH   | IIC   |     |

|          |                         |          |                                                |                          |        |        |     |      |       | 1                     | ICON  |        |      |       |       |       |               |        |       |     |

|          |                         |          | SIZE                                           | COL                      | DE IDE | ENT. N |     |      |       | DW                    | S NO. |        | •    | 100   | 14 0  |       | E             |        |       |     |

|          |                         |          | Α                                              |                          |        | 16     | 236 |      |       |                       |       |        |      | 162   | 2/12  | 203   | <b>၁</b>      |        |       |     |

|          |                         |          | REV                                            |                          |        |        |     |      |       | PAG                   | E 1   | OF     | 16   |       |       |       |               |        |       |     |

|          |                         |          |                                                |                          |        |        |     |      |       |                       |       |        |      |       |       |       |               |        |       |     |

AMSC N/A 5962-V097-12

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance 16 channel, 1 million samples per second (MSPS), 12 bit analog to digital converter with sequencer microcircuit, with an operating temperature range of -55°C to +125°C.

- 1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

V62/12635

01

X

B

Drawing number

Device type (See 1.2.1)

Case outline (See 1.2.2)

Lead finish (See 1.2.3)

1.2.1 Device type(s).

Device type Generic Circuit function

O1 AD7490-EP 16 channel, 1 MSPS, 12 bit analog to digital converter with sequencer

1.2.2 <u>Case outline(s)</u>. The case outline(s) are as specified herein.

Outline letter

Number of pins

JEDEC PUB 95

Package style

X

28

MO-153-AE

Plastic thin shrink small outline

1.2.3 <u>Lead finishes</u>. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

Finish designator

A Hot solder dip

B Tin-lead plate

C Gold plate

D Palladium

E Gold flash palladium

Z Other

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |

|                       |      | REV            | PAGE 2           |

# 1.3 Absolute maximum ratings. 1/

|     | Supply voltage (V <sub>DD</sub> ) to ground (GND)                              | -0.3 V to +7 V                                  |

|-----|--------------------------------------------------------------------------------|-------------------------------------------------|

|     | Logic power supply input (VDRIVE) to GND                                       | -0.3 V to $V_{\mbox{\scriptsize DD}}$ + 0.3 V   |

|     | Analog input voltage to GND                                                    | -0.3 V to V <sub>DD</sub> + 0.3 V -0.3 V to 7 V |

|     | Digital output voltage to GND                                                  | -0.3 V to $V_{\mbox{DD}}$ + 0.3 V               |

|     | Reference input (REFIN) to GND                                                 | ±10 m A <u>2</u> /                              |

|     | Junction temperature range (T <sub>J</sub> )                                   | 150°C                                           |

|     | Storage temperature range (T <sub>STG</sub> )<br>Lead temperature, soldering : |                                                 |

|     | Vapor phase (60 seconds) Infrared (15 seconds) Electrostatic discharge (ESD)   | 220°C                                           |

| 1.4 | Recommended operating conditions. 3/ 4/                                        | T KV                                            |

|     | Supply voltage (V <sub>DD</sub> ) range                                        | +4.75 V to +5.25 V                              |

|     | Operating free-air temperature range (T <sub>A</sub> )                         |                                                 |

| 1.5 | Thermal characteristics.                                                       |                                                 |

|     | Thermal impedance, junction to case(θ <sub>JC</sub> )                          | 14°C/W                                          |

|     | Thermal impedance, junction to ambient (θJA)                                   | 97.9°C/W                                        |

<sup>4/</sup> All ratings and specifications, please refer to the relevant manufacturer's EP datasheet.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |  |

|-----------------------|------|----------------|------------------|--|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |  |  |

|                       |      | REV            | PAGE 3           |  |  |

Stresses beyond those listed under "absolute maximum rating" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>2/</sup> Transient currents of up to 100 mA do not cause silicon controlled rectifier (SCR) latch up.

Use of this product beyond the manufacturers design rules or stated parameters is done at the user's risk. The manufacturer and/or distributor maintain no responsibility or liability for product used beyond the stated limits.

#### 2. APPLICABLE DOCUMENTS

JEDEC PUB 95 - Registered and Standard Outlines for Semiconductor Devices

(Applications for copies should be addressed to the Electronic Industries Alliance, 2500 Wilson Boulevard, Arlington, VA 22201-3834 or online at http://www.jedec.org)

## 3. REQUIREMENTS

- 3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

- 3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

- 3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 <u>Design, construction, and physical dimension</u>. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

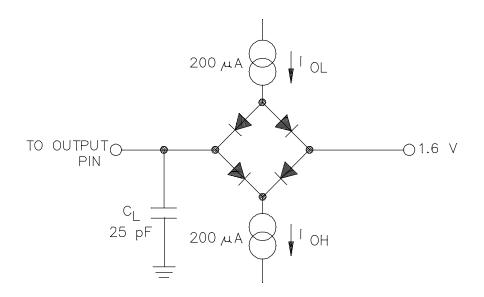

- 3.5.1 <u>Load circuit for digital output timing specifications</u>. The load circuit for digital output timing specifications shall be as shown in figure 1.

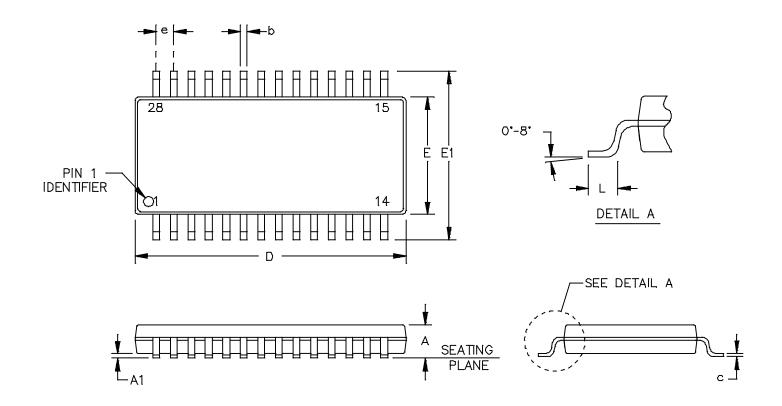

- 3.5.2 <u>Case outline</u>. The case outline shall be as shown in 1.2.2 and figure 2.

- 3.5.3 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 3.

| DLA LAND AND MARITIME |  | CODE IDENT NO. | DWG NO.          |

|-----------------------|--|----------------|------------------|

| COLUMBUS, OHIO        |  | <b>16236</b>   | <b>V62/12635</b> |

|                       |  | REV            | PAGE 4           |

TABLE I. Electrical performance characteristics. 1/

| Test                                 | Symbol | Conditions 2/                                                     | Temperature,    | Device<br>type | Lin         | nits   | Unit |

|--------------------------------------|--------|-------------------------------------------------------------------|-----------------|----------------|-------------|--------|------|

|                                      |        |                                                                   | - 7             |                | Min         | Max    |      |

| Dynamic performance                  |        |                                                                   |                 |                |             |        |      |

| Signal to (noise + distortion)       | SINAD  | f <sub>IN</sub> = 50 kHz sine wave,<br>f <sub>SCLK</sub> = 20 MHz | -55°C to +125°C | 01             | 69          |        | dB   |

| Signal to noise ratio                | SNR    |                                                                   | -55°C to +125°C | 01             | 69.5        |        | dB   |

| Total harmonic distortion            | THD    |                                                                   | -55°C to +125°C | 01             |             | -74    | dB   |

| Peak harmonic or spurious noise      | SFDR   |                                                                   | -55°C to +125°C | 01             |             | -75    | dB   |

| Intermodulation distortion           | IMD    | fa = 40.1 kHz, fb = 41.5 kHz                                      |                 |                |             |        |      |

| Second order terms                   |        |                                                                   | -55°C to +125°C | 01             | -85 ty      | ypical | dB   |

| Third order terms                    |        |                                                                   | -55°C to +125°C | 01             | -85 typical |        | dB   |

| Aperture delay                       |        |                                                                   | -55°C to +125°C | 01             | 10 typical  |        | ns   |

| Aperture jitter                      |        |                                                                   | -55°C to +125°C | 01             | 50 typical  |        | ps   |

| Channel to channel isolation         |        | f <sub>IN</sub> = 400 kHz                                         | -55°C to +125°C | 01             | -82 typical |        | dB   |

| Full power bandwidth                 | FPBW   | 3 dB                                                              | -55°C to +125°C | 01             | 8.2 ty      | ypical | MHz  |

|                                      |        | 0.1 dB                                                            |                 |                | 1.6 ty      | ypical |      |

| DC accuracy                          |        |                                                                   |                 |                |             |        |      |

| Resolution                           |        |                                                                   | -55°C to +125°C | 01             | 12          |        | Bits |

| Integral nonlinearity                |        |                                                                   | -55°C to +125°C | 01             |             | ±1     | LSB  |

| Differential nonlinearity            |        | Guaranteed no missed codes to 12 bits                             | -55°C to +125°C | 01             | -0.95       | +1.5   | LSB  |

| 0 V to REF <sub>IN</sub> input range |        | Straight binary output coding                                     |                 |                |             |        |      |

| Offset error                         |        |                                                                   | -55°C to +125°C | 01             |             | ±8     | LSB  |

| Offset error match                   |        |                                                                   | -55°C to +125°C | 01             |             | ±0.5   | LSB  |

| Gain error                           |        |                                                                   | -55°C to +125°C | 01             |             | ±2     | LSB  |

| Gain error match                     |        |                                                                   | -55°C to +125°C | 01             |             | ±0.6   | LSB  |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |  |

|-----------------------|------|----------------|------------------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |  |

|                       |      | REV            | PAGE 5           |  |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                     | Symbol          | Conditions 2/                                                                                                            | Temperature,    | Device<br>type                                 | Li   | Unit                     |     |  |

|------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------|------|--------------------------|-----|--|

|                                          |                 |                                                                                                                          | - 7             |                                                | Min  | Max                      |     |  |

| DC accuracy - continued                  | d.              |                                                                                                                          | •               |                                                |      |                          |     |  |

| 0 V to 2 x REF <sub>IN</sub> input range |                 | -REF <sub>IN</sub> to +REF <sub>IN</sub> biased about<br>REF <sub>IN</sub> with two's complement<br>output coding offset |                 |                                                |      |                          |     |  |

| Positive gain error                      |                 |                                                                                                                          | -55°C to +125°C | 01                                             |      | ±2                       | LSB |  |

| Positive gain error match                |                 |                                                                                                                          | -55°C to +125°C | 01                                             |      | ±0.5                     | LSB |  |

| Zero code error                          |                 |                                                                                                                          | -55°C to +125°C | 01                                             |      | ±8                       | LSB |  |

| Zero code error match                    |                 |                                                                                                                          | -55°C to +125°C | 01                                             |      | ±0.5                     | LSB |  |

| Negative gain error                      |                 |                                                                                                                          | -55°C to +125°C | 01                                             |      | ±1                       | LSB |  |

| Negative gain error match                |                 |                                                                                                                          | -55°C to +125°C | 01                                             |      | ±0.5                     | LSB |  |

| Analog input.                            |                 |                                                                                                                          |                 |                                                |      |                          |     |  |

| Input voltage range                      | VIN             | Range bit set to 1                                                                                                       | -55°C to +125°C | 01                                             | 0    | REFIN                    | V   |  |

|                                          |                 | Range bit set to 0                                                                                                       |                 |                                                | 0    | 2 x<br>REF <sub>IN</sub> |     |  |

| DC leakage current                       |                 |                                                                                                                          | -55°C to +125°C | 01                                             |      | ±1                       | μΑ  |  |

| Input capacitance                        | C <sub>IN</sub> |                                                                                                                          | -55°C to +125°C | 01                                             | 20 t | ypical                   | pF  |  |

| Reference input.                         | I .             | I                                                                                                                        | 1               | <u>ı                                      </u> |      |                          |     |  |

| REF <sub>IN</sub> input voltage          |                 | ±1% specified performance                                                                                                | -55°C to +125°C | 01                                             | 2.5  | typical                  | V   |  |

| DC leakage current                       |                 |                                                                                                                          | -55°C to +125°C | 01                                             |      | ±1                       | μΑ  |  |

| REF <sub>IN</sub> input impedance        |                 | f <sub>SAMPLE</sub> = 1 MSPS                                                                                             | -55°C to +125°C | 01                                             | 36 t | ypical                   | kΩ  |  |

| DLA LAND AND MARITIME |  | CODE IDENT NO. | DWG NO.          |

|-----------------------|--|----------------|------------------|

| COLUMBUS, OHIO        |  | <b>16236</b>   | <b>V62/12635</b> |

|                       |  | REV            | PAGE 6           |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                    | Symbol             | Conditions 2/                               | Temperature,<br>T <sub>A</sub> | Device<br>type | Lin                         | nits                        | Unit |

|-----------------------------------------|--------------------|---------------------------------------------|--------------------------------|----------------|-----------------------------|-----------------------------|------|

|                                         |                    |                                             |                                |                | Min                         | Max                         |      |

| Logic inputs.                           |                    |                                             |                                |                |                             |                             |      |

| Input high voltage                      | VINH               |                                             | -55°C to +125°C                | 01             | 0.7 x<br>V <sub>DRIVE</sub> |                             | V    |

| Input low voltage                       | VINL               |                                             | -55°C to +125°C                | 01             |                             | 0.3 x<br>V <sub>DRIVE</sub> | V    |

| Input current                           | I <sub>IN</sub>    | V <sub>IN</sub> = 0 V or V <sub>DRIVE</sub> | -55°C to +125°C                | 01             |                             | ±1                          | μА   |

| Input capacitance 3/                    | C <sub>IN</sub> +  |                                             | -55°C to +125°C                | 01             |                             | 10                          | pF   |

| Logic outputs.                          |                    |                                             |                                |                |                             |                             |      |

| Output high voltage                     | V <sub>OH</sub>    | I <sub>SOURCE</sub> = 200 μA                | -55°C to +125°C                | 01             | V <sub>DRIVE</sub><br>- 0.2 |                             | V    |

| Output low voltage                      | V <sub>OL</sub>    | I <sub>SINK</sub> = 200 μA                  | -55°C to +125°C                | 01             |                             | 0.4                         | V    |

| Floating state leakage current          |                    | WEAK/TRI bit set to 0                       | -55°C to +125°C                | 01             |                             | ±10                         | μА   |

| Floating state 3/<br>output capacitance |                    | WEAK/TRI bit set to 0                       | -55°C to +125°C                | 01             |                             | 10                          | pF   |

| Output coding                           |                    | Coding bit set to 1                         | -55°C to +125°C                | 01             | Straight natural binary     |                             |      |

|                                         |                    | Coding bit set to 0                         | _                              |                | Two's complement            |                             |      |

| Conversion rate.                        | •                  |                                             | •                              |                |                             |                             |      |

| Conversion time                         |                    | 16 SCLK cycles, SCLK = 20 MHz               | -55°C to +125°C                | 01             |                             | 800                         | ns   |

| Track and hold                          |                    | Sine wave input                             | -55°C to +125°C                | 01             |                             | 300                         | ns   |

| acquisition time                        |                    | Full scale step input                       |                                |                |                             | 300                         |      |

| Throughput rate                         |                    |                                             | -55°C to +125°C                | 01             |                             | 1                           | MSPS |

| Power requirements.                     |                    |                                             |                                |                |                             |                             |      |

| Power supply input                      | V <sub>DD</sub>    |                                             | -55°C to +125°C                | 01             | 4.75                        | 5.25                        | V    |

| Logic power supply input                | V <sub>DRIVE</sub> |                                             | -55°C to +125°C                | 01             | 2.7                         | 5.25                        | V    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |

|                       |      | REV            | PAGE 7           |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                         | Symbol          | Conditions 2/                                          | Temperature,    | Device<br>type | Lir   | nits    | Unit |

|------------------------------|-----------------|--------------------------------------------------------|-----------------|----------------|-------|---------|------|

|                              |                 |                                                        | ^               |                | Min   | Max     |      |

| Power requirements - co      | ontinued.       |                                                        |                 |                |       |         |      |

| Power supply current         | I <sub>DD</sub> | Digital inputs = 0 V or V <sub>DRIVE</sub>             |                 |                |       |         |      |

| Normal mode (static)         |                 | SCLK on or off                                         | -55°C to +125°C | 01             | 600 t | ypical  | μА   |

| Normal mode<br>(operational) |                 | fSCLK = 20 MHz,<br>f <sub>S</sub> = maximum throughput | -55°C to +125°C | 01             |       | 2.5     | mA   |

| Auto standby mode            |                 | f <sub>SAMPLE</sub> = 500 kSPS                         | -55°C to +125°C | 01             | 1.55  | typical | mA   |

|                              |                 | Static                                                 |                 |                |       | 100     | μΑ   |

| Auto shutdown                |                 | f <sub>SAMPLE</sub> = 250 kSPS                         | -55°C to +125°C | 01             | 960 t | ypical  | μА   |

|                              |                 | Static                                                 |                 |                |       | 0.5     |      |

| Full shutdown mode           |                 | SCLK on or off                                         | -55°C to +125°C | 01             |       | 0.5     | μА   |

| Power dissipation .          |                 |                                                        |                 |                |       |         |      |

| Normal mode (operational)    |                 | f <sub>SCLK</sub> = 20 MHz                             | -55°C to +125°C | 01             |       | 12.5    | mW   |

| Auto standby mode (static)   |                 |                                                        | -55°C to +125°C | 01             |       | 460     | μW   |

| Auto shutdown mode (static)  |                 |                                                        | -55°C to +125°C | 01             |       | 2.5     | μW   |

| Full shutdown mode           |                 |                                                        | -55°C to +125°C | 01             |       | 2.5     | μW   |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |

|                       |      | REV            | PAGE 8           |

TABLE I. <u>Electrical performance characteristics</u> – Continued. <u>1</u>/

| Test                                                                              | Symbol            | Conditions 4/ | Temperature,<br>T <sub>A</sub> | Device<br>type | Lin            | nits | Unit |

|-----------------------------------------------------------------------------------|-------------------|---------------|--------------------------------|----------------|----------------|------|------|

|                                                                                   |                   |               |                                |                | Min            | Max  |      |

| Timing specification.                                                             | <u>5</u> /        |               |                                |                |                |      |      |

| Clock frequency 6/                                                                | f <sub>SCLK</sub> |               | -55°C to +125°C                | 01             | 10             |      | kHz  |

|                                                                                   |                   |               |                                |                |                | 20   | MHz  |

| Convert timing                                                                    | tCONVERT          |               | -55°C to +125°C                | 01             | 16 x<br>tsclk  |      |      |

| Minimum quiet timing required between bus relinquish and start of next conversion | tQUIET            |               | -55°C to +125°C                | 01             | 50             |      | ns   |

| CS to SCLK setup time                                                             | t <sub>2</sub>    |               | -55°C to +125°C                | 01             | 10             |      | ns   |

| Delay from CS 7/ until DOUT three state disabled                                  | t <sub>3</sub>    |               | -55°C to +125°C                | 01             |                | 14   | ns   |

| Delay from CS to 8/<br>DOUT valid                                                 | t <sub>3</sub> b  |               | -55°C to +125°C                | 01             |                | 20   | ns   |

| Data access time 7/<br>after SCLK falling<br>edge                                 | t <sub>4</sub>    |               | -55°C to +125°C                | 01             |                | 40   | ns   |

| SCLK low pulse width                                                              | t5                |               | -55°C to +125°C                | 01             | 0.4 x<br>tsclk |      | ns   |

| SCLK high pulse width                                                             | t <sub>6</sub>    |               | -55°C to +125°C                | 01             | 0.4 x<br>tsclk |      | ns   |

| SCLK to DOUT valid hold time                                                      | t <sub>7</sub>    |               | -55°C to +125°C                | 01             | 15             |      | ns   |

| SCLK falling edge 9/<br>to DOUT high<br>impedance                                 | t <sub>8</sub>    |               | -55°C to +125°C                | 01             | 15             | 50   | ns   |

| DIN setup time prior to SCLK falling edge                                         | tg                |               | -55°C to +125°C                | 01             | 20             |      | ns   |

| DIN hold time after<br>SCLK falling edge                                          | t <sub>10</sub>   |               | -55°C to +125°C                | 01             | 5              |      | ns   |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |

|                       |      | REV            | PAGE 9           |

TABLE I. <u>Electrical performance characteristics</u> - Continued. <u>1</u>/

| Test                                                                  | Symbol             | Conditions 4/ | Temperature,<br>T <sub>A</sub> | Device<br>type | Lin | nits | Unit |

|-----------------------------------------------------------------------|--------------------|---------------|--------------------------------|----------------|-----|------|------|

|                                                                       |                    |               | , .                            |                | Min | Max  |      |

| Timing specification con                                              | tinued. <u>5</u> / |               |                                |                |     |      |      |

| 16th SCLK falling edge to CS high                                     | t <sub>11</sub>    |               | -55°C to +125°C                | 01             | 20  |      | ns   |

| Power up time from full power down/ auto shutdown/ auto standby modes | t <sub>12</sub>    |               | -55°C to +125°C                | 01             |     | 1    | μ\$  |

- 1/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

- Unless otherwise specified, V<sub>DD</sub> = 4.75 V to 5.25 V, V<sub>DRIVE</sub> = 2.7 V to 5.25 V, REF<sub>IN</sub> = 2.5 V, and f<sub>SCLK</sub> = 20 MHz. Specifications apply for fSCLK up to 20 MHz. However, for serial interfacing requirements, see manufacturer's datasheet.

- 3/ Guaranteed by characterization.

- $\underline{4}$ / Unless otherwise specified, V<sub>DD</sub> = 4.75 V to 5.25 V, V<sub>DRIVE</sub>  $\leq$  V<sub>DD</sub>, and REF<sub>IN</sub> = 2.5 V.

- Guaranteed by characterization. All input signals are specified with t<sub>R</sub> = t<sub>F</sub> = 5 ns (10% to 90% of V<sub>DD</sub>) and timed from a voltage level of 1.6 V, see figure 1.

- 6/ The mark/space ratio for the SCLK input is 40/60 to 60/40.

- Measured with the load circuit of figure 1 and defined as the time required for the output to cross 0.4 V or 0.7 VDRIVE.

- 8/ t<sub>3</sub>b represents a worst case figure for having ADD3 available on the DOUT line, that is, if the device goes back into three state at the end of conversion and some other device takes control of the bus between conversions, the user has to wait a maximum time of t<sub>3</sub>b before having ADD3 valid on the DOUT line. If the DOUT line is weakly driven to ADD3 between conversions, the user typically has to wait 12 ns at 5 V after the CS falling edge before seeing ADD3 valid on DOUT.

- g/ t<sub>8</sub> is derived from the measured by the data outputs to change 0.5 V when loaded with the circuit of figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 25 pF capacitor. This means that the time, t<sub>8</sub>, quoted in the timing characteristics, is the true bus relinquish time of the part and is independent of the bus loading.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |

|                       |      | REV            | PAGE 10          |

FIGURE 1. Load circuit for digital output timing specifications.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |

|                       |      | REV            | PAGE 11          |

FIGURE 2. Case outline.

| DLA LAND AND MARITIME | SIZE     | CODE IDENT NO. | DWG NO.          |

|-----------------------|----------|----------------|------------------|

| COLUMBUS, OHIO        | <b>A</b> | <b>16236</b>   | <b>V62/12635</b> |

|                       |          | REV            | PAGE 12          |

|        |          | Dimensions |        |        |  |  |

|--------|----------|------------|--------|--------|--|--|

| Symbol | Incl     | hes        | Millir | neters |  |  |

|        | Min      | Max        | Min    | Max    |  |  |

| А      |          | .047       |        | 1.20   |  |  |

| A1     | .001     | .005       | 0.05   | 0.15   |  |  |

| b      | .007     | .011       | 0.19   | 0.30   |  |  |

| С      | .003     | .007       | 0.09   | 0.20   |  |  |

| D      | .377     | .385       | 9.60   | 9.80   |  |  |

| E      | .169     | .177       | 4.30   | 4.50   |  |  |

| E1     | .251 BSC |            | 6.40   | BSC    |  |  |

| е      | .025 BSC |            | 0.65   | BSC    |  |  |

| L      | .017     | .029       | 0.45   | 0.75   |  |  |

# NOTES:

- Controlling dimensions are millimeter, inch dimensions are given for reference only.

Falls within reference to JEDEC MO-153-AE.

FIGURE 2. <u>Case outline</u> - Continued.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |

|                       |      | REV            | PAGE 13          |

| Device type     |                    | 01                 |                    |

|-----------------|--------------------|--------------------|--------------------|

| Case outline    |                    | Х                  |                    |

| Terminal number | Terminal symbol    | Terminal<br>number | Terminal symbol    |

| 1               | V <sub>IN</sub> 11 | 15                 | DOUT               |

| 2               | V <sub>IN</sub> 10 | 16                 | SCLK               |

| 3               | V <sub>IN</sub> 9  | 17                 | V <sub>DRIVE</sub> |

| 4               | NC                 | 18                 | NC                 |

| 5               | V <sub>IN</sub> 8  | 19                 | DIN                |

| 6               | V <sub>IN</sub> 7  | 20                 | CS                 |

| 7               | V <sub>IN</sub> 6  | 21                 | AGND               |

| 8               | V <sub>IN</sub> 5  | 22                 | V <sub>DD</sub>    |

| 9               | V <sub>IN</sub> 4  | 23                 | REFIN              |

| 10              | V <sub>IN</sub> 3  | 24                 | AGND               |

| 11              | V <sub>IN</sub> 2  | 25                 | V <sub>IN</sub> 15 |

| 12              | V <sub>IN</sub> 1  | 26                 | V <sub>IN</sub> 14 |

| 13              | V <sub>IN</sub> 0  | 27                 | V <sub>IN</sub> 13 |

| 14              | AGND               | 28                 | V <sub>IN</sub> 12 |

FIGURE 3. Terminal connections.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |

|                       |      | REV            | PAGE 14          |

| Terminal symbol                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS                                      | Chip select. Active low logic input. This input provides the dual function of initiating conversions on the device and also frames the serial data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| REFIN                                   | Reference input for the device. An external reference must be applied to this input. The voltage range for the external reference is 2.5 V $\pm$ 1% for specified performance.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>DD</sub>                         | Power supply input. The V <sub>DD</sub> range for the device is from 2.7 V to 5.25 V. For the 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| . 55                                    | to 2 x REF <sub>IN</sub> range, V <sub>DD</sub> should be from 4.75 V to 5.25 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AGND                                    | Analog ground. Ground reference point for all circuitry on the device. All analog/digital input signals and any external reference signal should be referred to this AGND voltage. All AGND pins should be connected together.                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>IN</sub> 0 to V <sub>IN</sub> 15 | Analog input 0 through analog input 15. Sixteen single ended analog input channels that are multiplexed into the on chip track and hold. The analog input channel to be converted is selected by using the address bits ADD3 through ADD0 of the control register. The address bits, in conjunction with the SEQ and SHADOW bits, allow the sequence register to be programmed. The input range for all input channels can extend from 0 V to REFIN or 0 V to 2 x REFIN as selected via the RANGE bit in the control register. Any used input channels should be connected to AGND to avoid noise pickup. |

| DIN                                     | Data in. Logic input. Data to be written to the control register of the device is provided on this input and is clocked into the register on the falling edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DOUT                                    | Data out. Logic out. The conversion result from the device is provided on this output as serial data stream. The bits are clocked out on the falling edge of the SCLK input. The data stream consists of four address bits indicating which channel the conversion result corresponds to, followed by the 12 bits of conversion data, which is provided by MSB first. The output coding can be selected as straight binary or twos complement via the CODING bit in the control register.                                                                                                                 |

| SCLK                                    | Serial clock. Logic input. SCLK provides the serial clock for accessing data from the part. This clock input is also used as the clock source for the conversion process of the device.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>DRIVE</sub>                      | Logic power supply input. The voltage supplied at this pin determines at what voltage the serial interface of the device operates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

FIGURE 3. <u>Terminal connections</u> - continued.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |

|                       |      | REV            | PAGE 15          |

#### 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

## 5. PREPARATION FOR DELIVERY

- 5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

- 6. NOTES

- 6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

- 6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

- 6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <a href="http://www.landandmaritime.dla.mil/Programs/Smcr/">http://www.landandmaritime.dla.mil/Programs/Smcr/</a>.

| Vendor item drawing administrative control number 1/ | Device<br>manufacturer<br>CAGE code | Vendor part number |

|------------------------------------------------------|-------------------------------------|--------------------|

| V62/12635-01XB                                       | 24355                               | AD7490SRU-EP-RL7   |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

<u>CAGE code</u> <u>Source of supply</u>

24355 Analog Devices

Route 1 Industrial Park P.O. Box 9106 Norwood, MA 02062

Point of contact: Raheen Business Park Limerick, Ireland

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/12635</b> |

|                       |      | REV            | PAGE 16          |